身为一位专注于嵌入式系统研发的工程师,我对LS1043DDR的设计研究始终视为工作中最为关键的课题之一。LS1043DDR作为一款运行速度快且能耗较低的微处理器,其复杂的设计包括硬件电路结构设计、PCB排布以及DDR控制器设置等多层次内容。今日本文将详细阐述我在LS1043DDR设计过程中所积累的宝贵经验与心得体会。

1.LS1043DDR设计的背景

由恩智浦(NXP)研发的LS1043DDR作为一款专用嵌入式处理器,适用于网络通讯与工业控制等众多领域。其高效能且低能耗特性深受业界赞誉。在实际设计过程中,根据具体项目需求精准选用DDR类型、速度以及设置是充分发挥LS1043DDR效用的关键所在。

在细察LS1043DDR之设计前,需熟知处理器之技术说明书,涵盖其能支持的DDR类别、频段及电性特性等细节。此外,结合实际运用环境,甄选出合适之DDR芯片与PCB布局策略,以确保系统之稳定可靠。

在设计环节,需充分考量功耗与散热问题,合理配置供电电路及散热措施,保障系统的长期稳定运行。此外,亦需重视信号完整性与时序逻辑,防止因时序偏差或信号干扰而引发系统故障。

2.DDR控制器配置

DDR控制器乃LS1043DDR系列之核心组件,其设定对整个系统的性能及稳定性起着至关重要的作用。为确保最佳性能,需依据DDR内存晶片规格与处理器需求,精准调整时序、校准及控制等各类参数数值。

在设定DDR控制器时需谨慎调整其时序参数,如时钟频率、时序延迟以及时序校准,同时兼顾预充电、自刷新及写入级联等功能的配置,确保其高效运行与最佳性能表现。

在精准配置阶段,主要依赖于仿真工具以确保时序逻辑符合规范,从而规避时序矛盾以及数据误码率。经过多次微调与优化,终将使DDR控制器维持稳健运营并发挥其卓越性能。

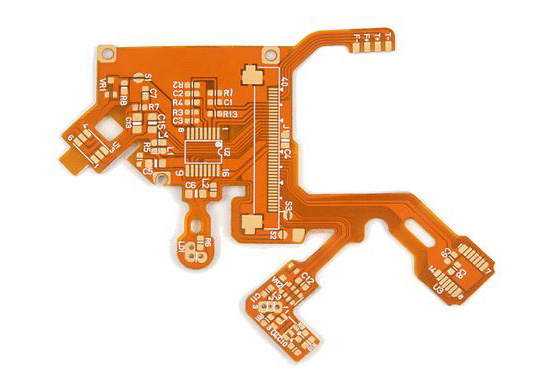

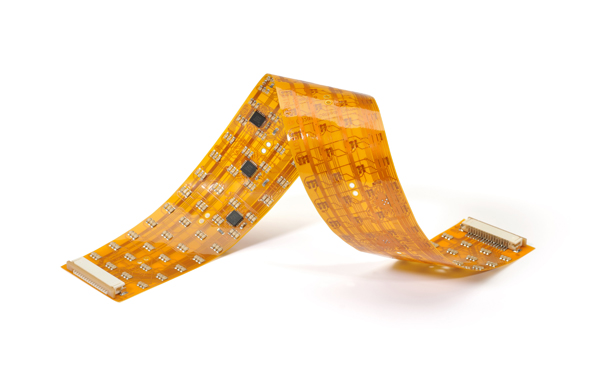

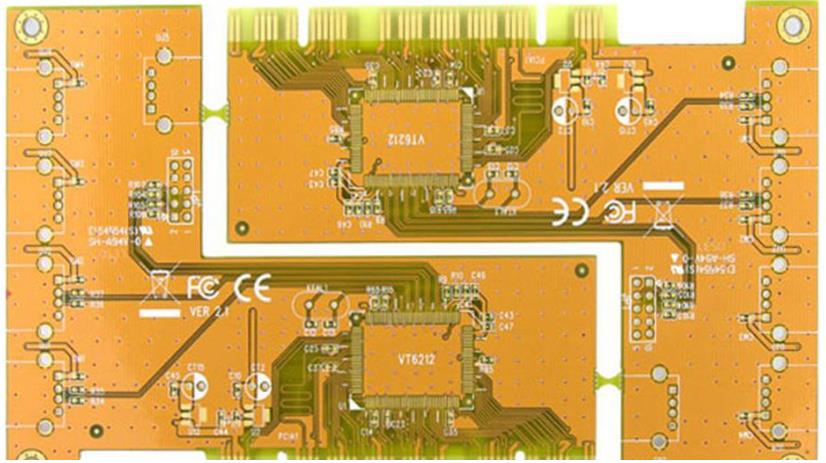

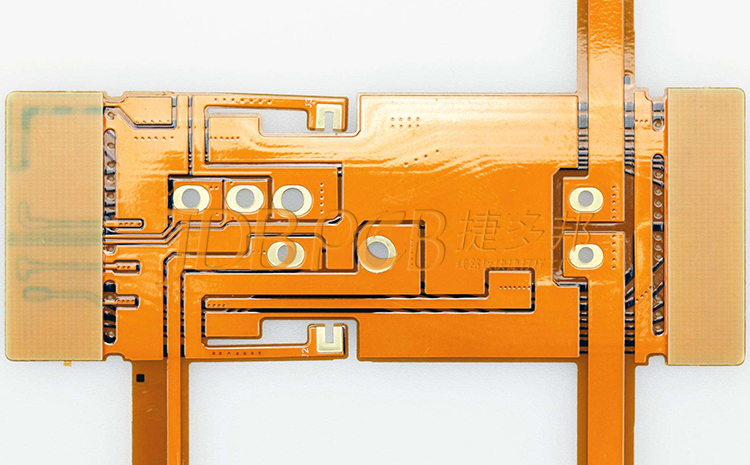

3.PCB布局设计

在LS1043DDR设计过程中的关键环节即为PCB布局设计,合理的布局可降低信号干扰并提升信号质量,以此确保整体性能及稳定运行。在执行此项工作时需重点关注以下几点:

排布时应利用处理器与DDR芯片的位置优势,优化信号线规划,以减小时序延迟及信号传输距离,降低信号失真的风险;其次,需确保信号线与电源线的隔离,防止相互干扰,保障系统稳定运行。

需特别留意地线与电源线布局以维持稳定的地电位及电源电位,并降低地回流与电磁干扰的负面效应。另外,在处理差分信号布局问题上,必须确保差分对的匹配度,避免因差分信号失真的发生而引发通讯误差。

4.调试与验证

在完成LS1043DDR设计之后,调试与验证环节显得尤为关键,通过这两步操作,我们能有效地找出可能存在的问题,完善并优化设计策略,进而保障整个系统能够顺利运作。在此期间,我们需关注以下几大要点:

首先,透过获取并分析DDR控制器的状态寄存器与性能计数器信息,我们能实时洞察DDR控制器的运作状况及性能参数,便于及时发现并解决可能存在的问题。其次,借助于外接示波器对信号波形进行监测,以核实时序关联及信号完整性,从而保证信号品质达到既定需求。

此外,时序校准与数据校验过程中,借助软件工具及硬件测试点可对时序关联性及数据传输精确度进行核实。最后,为全面审视系统性能及稳定状况,采用测试程序及应用程序进行操作,以便发现并解决可能存在的问题。

5.总结与展望

LS1043DDR设计乃是一个极具挑战性的项目,须涵盖诸多环节,如硬体设计、软件配备及调试验证等。在不断的学习与实践中,我逐渐领悟到了LS1043DDR设计的关键之处以及相关注意点,使自身的嵌入式系统设计技能得到显著提升。

在可预见的未来,我将全力投入到嵌入式系统设计的钻研与提高中,致力于为各类项目输送更高层次的专业技术支持。期望通过自身不懈的努力,能研发出更具稳定性与高效性的嵌入式系统,从而推动整个行业及科技领域的持续发展。