身为一名嵌入式系统工程师,我时常遭遇各种难题与困境,其中一大挑战便是Zynq写入DDR速度不足的现象。实践操作过程中,DDR存储装置的读写速度关乎系统效率及应答时间,故而彻底解决Zynq写入DDR速度不足的问题显得尤为关键。本文将分享本人的一些实践经验与心得体会,期望能为同样面临此类问题的同行提供参考。

了解Zynq写DDR速度不够的原因

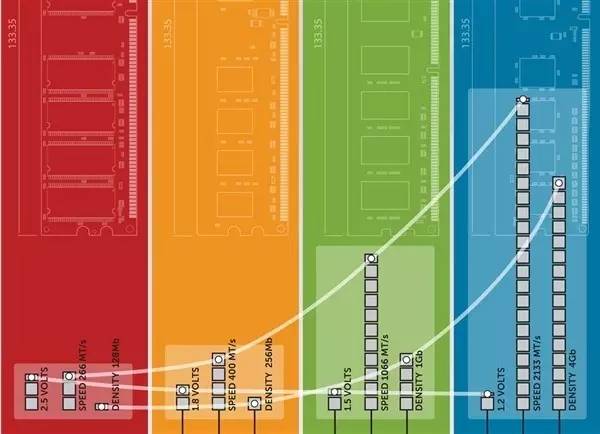

对于Zynq设备中DDR读写速度不足现象需以深刻理解其成因作为首要措施,具体来说,存储器速度受到各类复杂因素如时序设计欠妥、信号完整性不佳以及频率设定不适等人为因素影响。经过详细研究与实践,我们发现时序设计偏差是导致写入数据时序不稳,进而影响DDR写入速度的主要原因。因此,解决此问题的关键在于对时序进行严谨的分析及调整,使之满足规范标准。

信号完整性问题是DDR写入速度受限的主要原因之一。在高带宽信号传输过程中,易受串扰与反射等影响而出现数据传输错误甚至速度减缓现象。为此,在DDR接口开发阶段,必须重视线路规划、信号平衡以及阻抗均衡等环节,以保证信号的完备性及稳定性。

优化DDR写入速度的方法

为了解决Zynq设备中DDR读写速度不足的问题,我们可以实施以下几项有效的优化对策。首先,通过系统化的时序设定与频率调节,能大幅度提升DDR的写入性能。其次,在制定具体的时序方案时,运用相关软件进行精确的分析和设定,以此保证时序符合规格,进一步提升数据传输速率。再者,针对DDR的运行频率进行适度调整,提高时钟频率,也能达到同样的效果。

此外,布线与信号完整性的改善亦可提升DDR的写入速度。精心设计的布线方案及良好的信号匹配,能降低信号传输中的干扰与反射现象,进而提升信号质量与稳定性,实现更快的写入速度。同时,差分信号传输以及终端匹配等技术手段也被广泛应用,以进一步增强信号完整性,保证数据传输的精确度与速度。

调试Zynq写DDR速度不够的方法

在实际调试过程中,我们需将软硬兼施,综合运用多种方法来深度剖析并解决Zynq读写DDR速率不足的问题。首先,借助如逻辑分析仪之类的设备,我们能对时序进行严密检测与深入分析,从而定位出时序偏差的具体部位及其成因。其次,通过信号探测器对信号进行精确采样与细致分析,我们能够挖掘出信号完整性问题的根本源头,进而实施针对性的优化与调整措施。

此外,我们还能利用软件调试试探并改良DDR的写入效率。只需编写特定测试程序,对DDR进行读写实验,测量datatransferspeed及稳定性,定位可能存在的问题。在此基础上,适当调整软件设定,发挥数据传输过程的潜在优势,进一步提升写入速度与效益。

总结与展望

为了提高Zynq在DDR写入速率不足问题中的性能,我们必须从多角度进行细致而深度的分析与调试。这包括时序设计、信号完整性以及频率设定等关键因素。通过科学合理的调整与优化策略,能显著改善DDR写入速度,从而增强系统功能和响应速率。展望未来,我会持续深入学习并付诸实践,以期进一步优化系统性能,为项目的顺利推进和圆满落成尽我所能。