身为资深硬件工程师,我深切领悟到DDR5时序之于系统稳定性与性能所致之重要性。日常工作中所见之各种DDR5时序调试难题,推动我对其有更深层次的理解。在此篇文章中,我将从时序概念、时序参数、时序调试工具以及时序优化策略等多个角度进行阐述,期望能为各位解决DDR5时序问题提供参考与启示。

时序概念

理解DDR5时序原理至关重要。时序描述了数字系统中不同部件间信号传输所需时间,而DDR5内存则由多项时序参数组成,如频率、周期、延迟与传输速率等。这些因素不仅决定了存储器读写效率及稳定性能,更将极大地提升整个系统的运行效能。

DDR5时序中有几项颇具关键性的参数,如CL(CASLatency)、tRCD(RAStoCASDelay)、tRP(RowPrechargeTime)以及tWR(WriteRecoveryTime)等。它们的差异性选择将对内存的读写速率及延迟产生显著影响,因此需依据特定的硬件平台与实际应用环境进行科学设定与调整。

另外,DDR5时序涵盖了信号传输时间,时钟同步以及数据稳定性等知识。深刻理解这些晦涩的时序概念是解决DDR5时序问题的关键,有助于提升整个系统的性能及稳定性。

时序参数

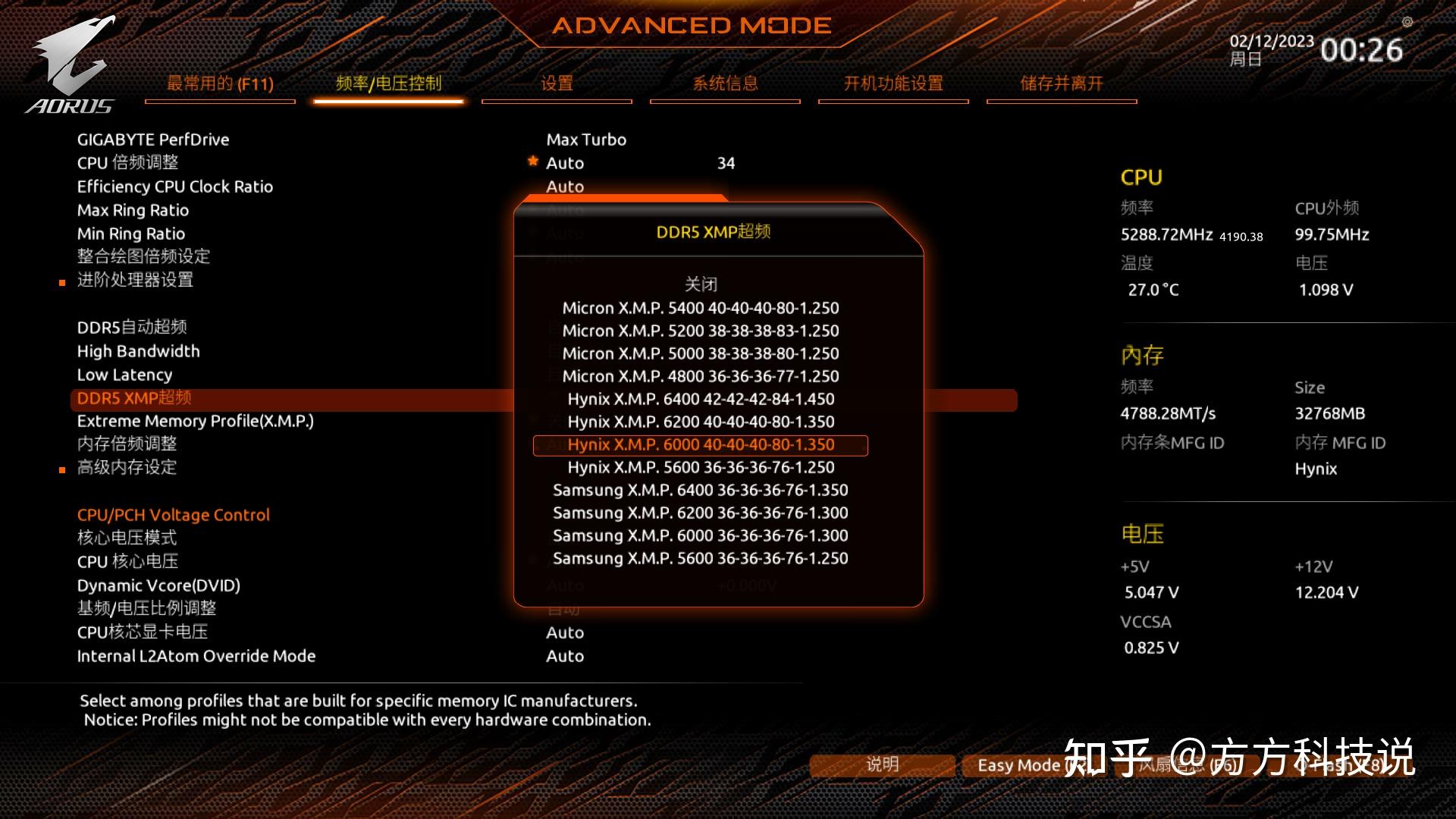

在DDR5技术体系中,精准设定及调试各个时序参数至关重要。因它们对系统整体性能与稳定性均有显著影响,故须谨慎微调各参量,以期实现最佳效果。

CL(CASLatency)即挂载着指令执行所需内存等待时间的时钟周期,这对于提升内存访问速度大有裨益,但亦有可能加重内存控制器负担。适宜的CL数值设定可助我们找寻性能与稳定之间的最佳平衡。

其次,tRCD(RAS至CAS延迟)代表了从行地址选通到列地址选通期间所占用的延迟时间。数值较小的tRCD有助于提升内存读写效率,然而亦有引发读取误差之风险,故在调试过程中须确保读数精确及稳定。

此外,依据实际环境相应调整的参数还包括:tRP(行预充电时间)以及tWR(写入恢复时间)。科学设定这些时序参数有助于提高内存系统的性能与稳定性,防止因时序问题引发的系统故障。

时序调试工具

在进行DDR5时序调整过程中,选择高效且灵活的工具至关重要。这些工具可助工程师精确而迅速地分析并修复时序问题,显著提升工作效率与调试水平。

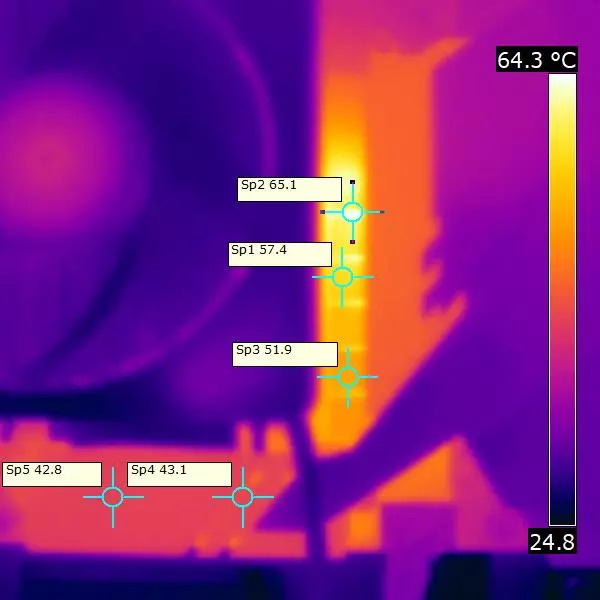

时序调试常用工具有逻辑分析仪、示波器及信号发生器。其中,逻辑分析仪可捕捉并剖析时序信号,协助工程师精准定位时序故障;示波器则能直观呈现信号间时序联系,辅助工程师了解信号稳定性与波形特质;而信号发生器则能产生各类时序信号,以供系统时序性能测试与验证之用。

除了硬件器械,有数种高效的软件工具能助力时序调试。譬如说,时序分析软件可协助工程师迅速掌握时序参数并排查潜在问题;而时序仿真工具则能精确模拟各种可能的时序环境,以指导工程师精确调整时序设定。这些软件工具的运用将大大简化时序调试过程,提升工程师的工作效能。

时序优化技巧

除了精准设定时序参数及运用时序调试设备之外,还可采取诸多高效时序优化措施协助技术人员妥善处理DDR5时序难题,从而显著提高系统运行效率与稳定性。

首要策略是妥善布置PCB电路并改善信号线,以实现系统时序的提升。优秀的PCB布局可缩短信号传输路线,降低信号延迟及失真,从而增强系统稳定性。对信号线进行精妙的优化可降低信号间的串扰与噪声,确保信息精确无误地传递。

次之,选用优质存储器芯片及内存控制装置,同样是实现时序优化的核心要素。优质芯片与控制器具备优异的时序特征及稳定性,可显著降低时序风险,提升系统性能。

此外,适时更新固件与驱动亦有助于改善时序稳定性。制造商将持续完善固件和驱动程序,修正已发现的时序问题并提高系统兼容性。适时更新可确保系统在时序控制方面更为稳定与可靠。

总结

本文针对DDR5时序问题进行深度分析后发现,时序在内存系统中占据核心地位,妥善设定与运用时序参数及调试工具,掌握有效的时序优化策略,皆为解决此类问题的重点。因此,深入理解定时概念,并持续进行实际操作与调试,方能赋予系统更高的性能与稳定性,规避由时序问题引发的系统故障及性能下滑现象。

在实际应用过程中,时序问题往往具有多种复杂性,这就要求工程师具备深厚的理论知识与丰富的实战经验,以有效应对并解决此类难题。期望本篇文章能对各位读者深入了解DDR5时序问题提供有益启示,使其于工程实践中更从容地应对时序挑战,进阶提升系统性能及稳定表现。