身为一位专注于电子工程领域的设计者,我对DDR封装基板走线有着深厚理解。DDR即“双倍数据速率”,其走线在电路板设计过程中,无疑扮演着决定性角色,因为它们直接关乎信号传送的稳定性与效率。本文将从走线基础知识、布局策略、信号完好性、差分对、电磁相容性、时序检视、噪音处理及实例研究等多角度出发,全方位解析该这一复杂议题,希望能为广大同行提供有益参考。

走线的基本原理

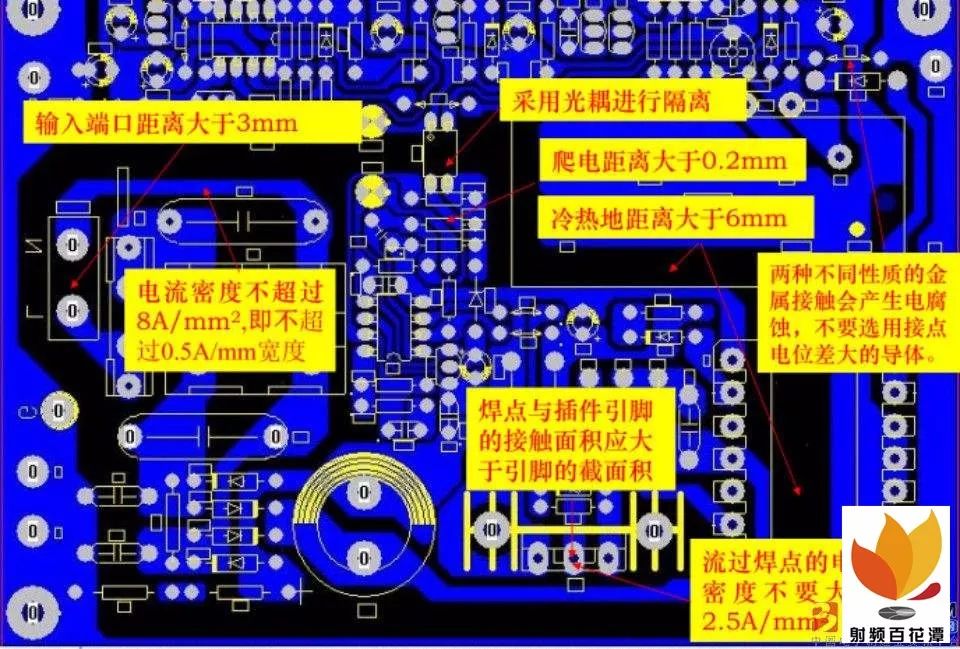

作为PCB设计至关重要的部分,了解走线设计原理至关重要。首先要理解信号在走线中的传输模式,如DDR封装基板中,走线参数如宽度、间距及层次布局等均会对信号速率与稳定度产生直接影响。为确保信号高速畅行,需遵守匹配阻抗、降低串扰、维持信号完整性的原则进行走线设计。同时,还应考虑信号层间转换与匹配延迟等因素,以保证信号精准传输。

在布设线路结构中,务必规划好信号线长度、差分对排列及路径走向。如此可减少信号间的干扰并提升信号的抗干扰性。同时,分布差分对时,需确保两条差分线上的长度相当,确保信号的同步传输。如此规划,有助于缩短信号传递延迟,从而增强了信号的稳定性。

布局技巧

DDR封装基板布线规划中,择优布势至为关键。首要须处理好各类线束间的布局问题。为此,务求减少线缆彼此交错,防止讯号串扰,同时保证讯号线整齐并行,降低干扰。

在布局设计中,需注意信号线长度及差分对彼此间位置的适宜设置。如此方能减少传输延时,有助于增强信号稳定度。同时,务必留意信号线路的阶层性规划,应将高速与低速信号线区别开来布置,以此降低信号间的串扰风险。

信号完整性

在高速存储器DDR的基板走线设计中,保证信号的完整性至关重要。这意味着在信号传输期间,其电平值与原始波形须无损,不受噪声和其他扰动的侵蚀。为达到此目的,须兼顾各个关键要素:信号线之间的匹配阻抗、线路长度的平衡以及差分对行列的合理布置等。

在执行信号完整性评估中,须进行时序与噪声分析等环节。时序分析可深入了解信号在传输阶段中的延迟及时钟偏移现象,确保信号的同步传输。同时,噪声分析则针对信号线所承受的干扰与噪声状况,进而采取针对性抑制策略,保障信号的稳定传输。

差分对

在DDR封装基板的线路安排设计过程中,差分对的摆放位置尤为关键。差分对作为一种常见的信息传输形式,通过把信号线与它的逆向线搭配构成双线来传输,进而减少干扰与噪音的影响。布置差分对时,务必注意使它们的线段等长且间隔适宜,从而保障信号的同步稳定传输。

除此之外,实施差分对布设时需着重考量其信号线路的方向以及层次结构。科学且严谨的差分对布设方式,能有效降低信号线间的串扰,进而增强信号的抗干扰能力;同时,借助分层差分对布设策略,能有效缩短信号线传输延迟,进一步提升信号的稳定性。

电磁兼容性

电磁兼容性作为DDR封装基板布线要素之一,至关重要。其旨在确保电路在受电磁影响下依旧能稳定运行,无电磁干扰行为及免受其害。设计时需考虑信号层排布、差分对安置以及防护措施等方面。

合理配置层次结构及使用差分对设计,能有效降低信号间串扰与干涉,从而提升信号抗干扰性能。借助于屏蔽技术,则可显著减轻外部电磁干扰对信号传播的影响,确保信号稳定传送。综合考虑上述各要素,有望大幅度提升DDR封装基板的电磁兼容水平。

时序分析

时序分析在DDR封装基板走线设计中至关重要。此分析旨在解析信号传递期间产生的延时而非实时传输,考量因素包括信号线长度的匹配性、差分对位置以及时钟信号的传送等。

借助时序分析技术,我们可发现并解决信号传递中的延迟及时钟偏移问题,适时调整设计策略以保证信号同频传递。与此同时,时序分析亦能帮助我们识别和修复可能出现的时序违规情况,保障信号稳定传送。

噪声抑制

在DDR封装基板布线设计上,抑制噪音乃是重中之重。所谓噪,乃是信号传播之时所遭受之干涉及杂音,势必导致信号传输稳定性下降。因此,为抑制噪音,须考虑信号线路匹敌阻抗、差分对配置以及屏蔽设置等关键要素。

凭借精准的阻抗配置与差分线排版,可有效减轻信号线路所受干扰及噪声,提升抗扰性;借助有效的屏蔽设计,可大幅度降低外界干扰对信号传输的不良影响,从而保障信号稳定输送。全面统筹以上诸项因素,便能成功应对潜在DDR封装基板走线噪声问题。

实际案例

在实践的DDR封装基板线路规划实例中,我们可透过具体部署加深理解。例如,某款DDR封装基板的线路规划不当,引发了信号间严重的干扰问题,进而影响数据传输速率与稳定性。对此,重新调整信号路径,优化差分对配置及分层布设,成功解决了信号传输中的串扰问题,保障了数据的稳健传输。

透过实例分析,我们能深入掌握DDR封装基板走线设计要领,为实际运作中的走线制定提供有力参考。