身为一名电子工程师,DDR总线布线规则始终占据着我工作的核心位置。DDR(双倍数据速率)作为一种普遍使用的存储器类型,其总线布线规则乃是保障内存及处理器间高速信息传递的要件。在日常工作中,我对DDR总线布线规则的关键性深有感触,现将我对此的心得体会加以阐述。

DDR总线走线规则的基本概念

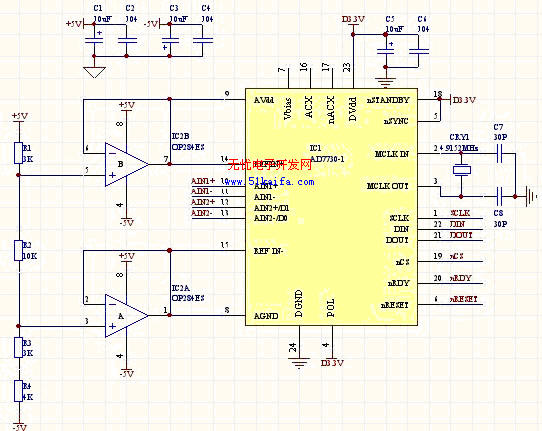

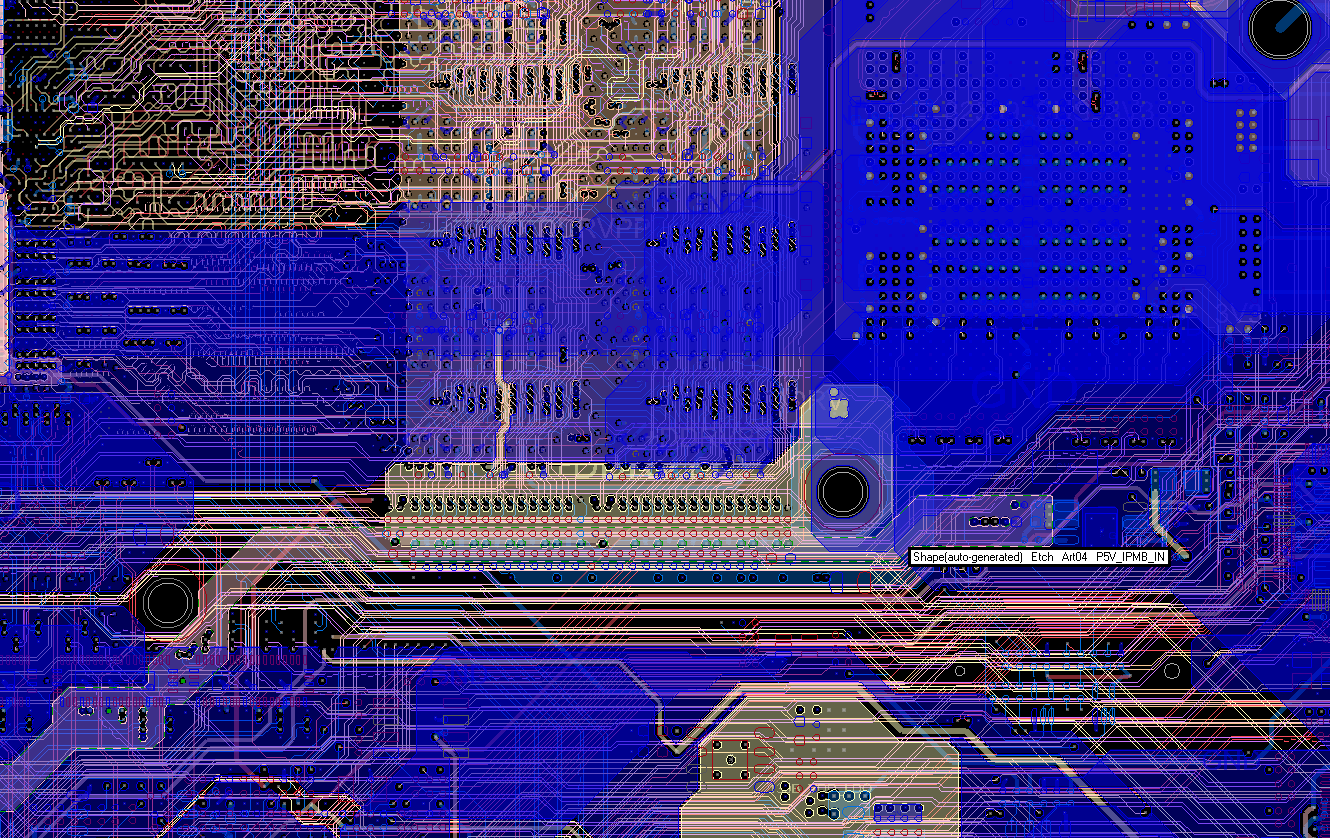

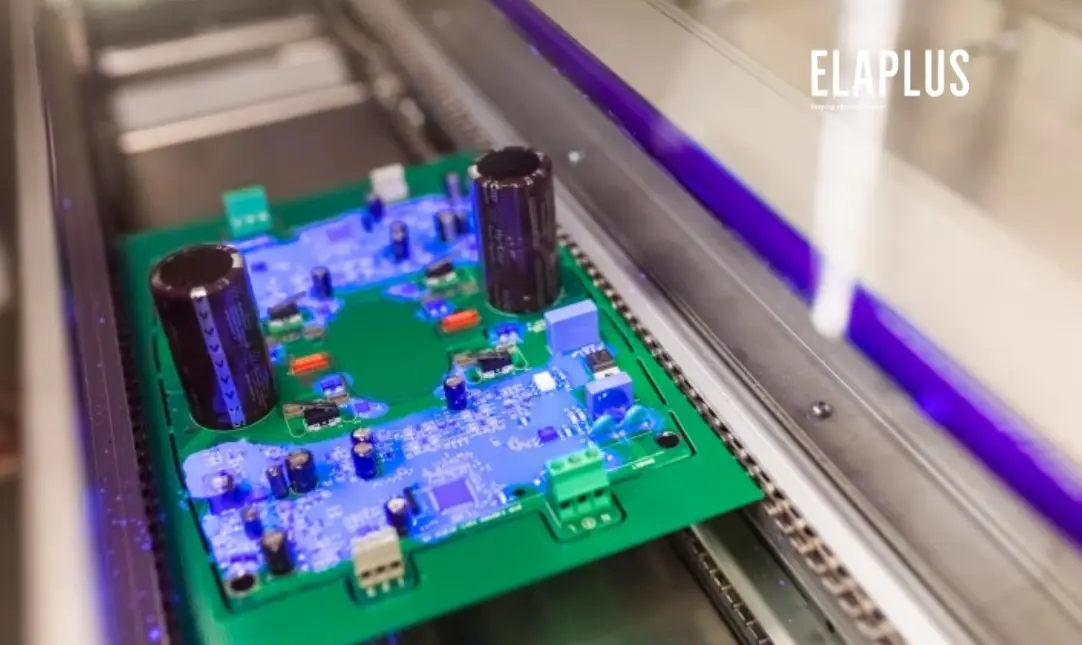

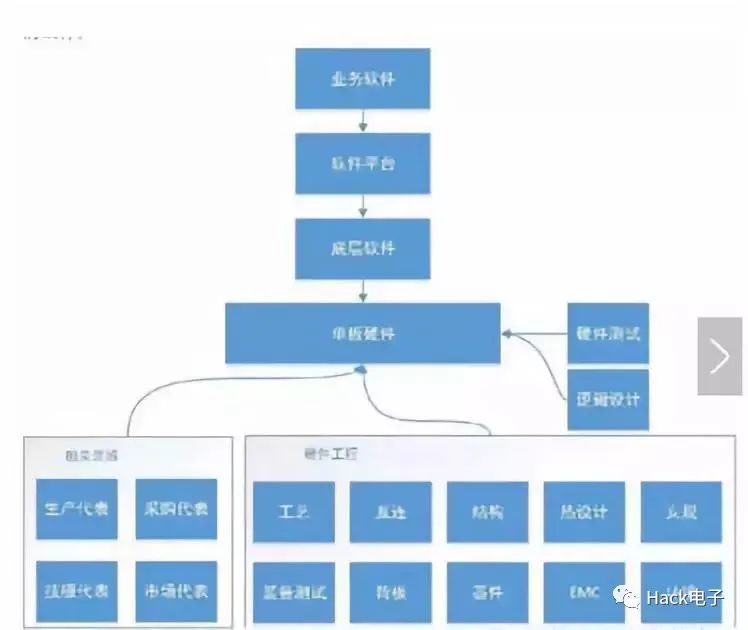

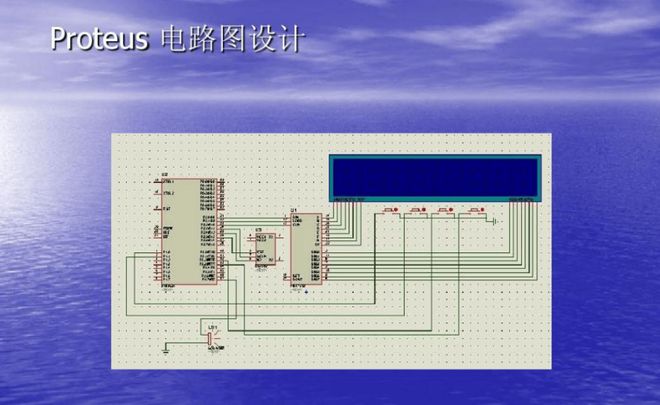

在电路板设计中,为保证信号稳定可靠地传输,必须遵从DDR总线走线规范,这包括了线路长度、匹配度、层间间距以及阻抗控制等多方面的详细要求。遵循这些规范,能有效减少信号反射与串扰现象,进而提升整个系统的性能及稳定性。

实践中的DDR总线线路治则需依据特定DDR版本与频率进行调整,以便适配各类不同的DDR内存需求。优秀的线路规则制定能有效提升内存数据传输速率,降低能耗,规避系统问题,成为保障系统稳定运行的基石关键。

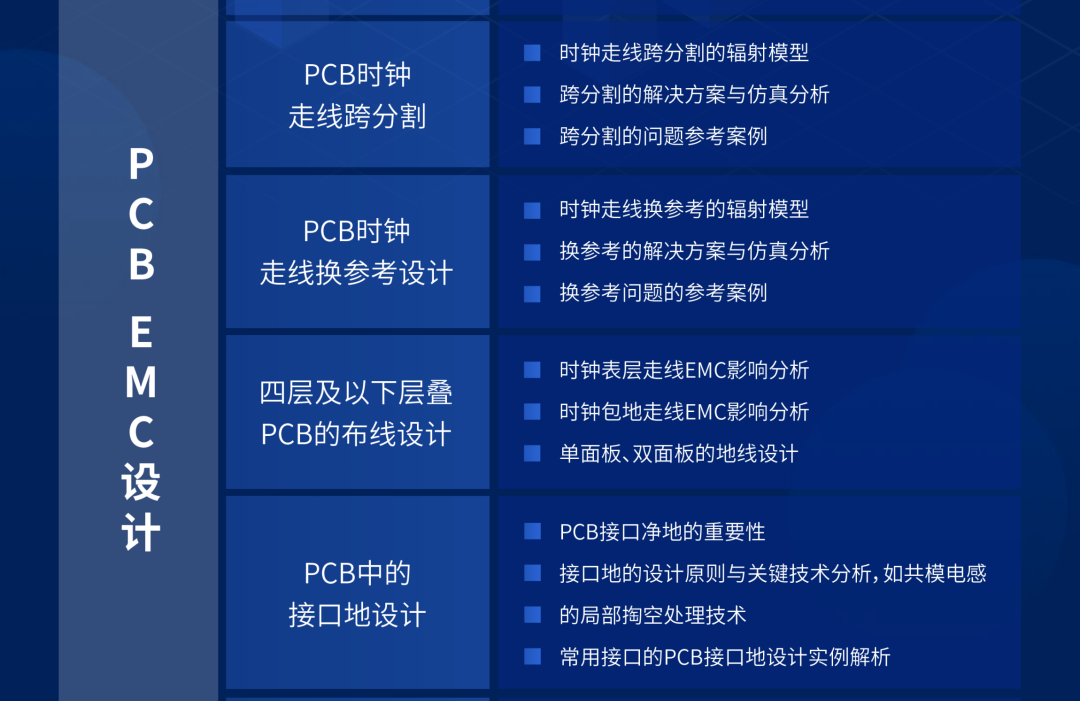

DDR总线走线规则的关键影响因素

走线长度匹配要求:在DDR总线上,数据线与控制线需保持相应的比例,确保信号同时达到目的地址,有效避免时序误差,从而保障数据传输精确度。

层间距离设定:在电路板的设计过程中,必须严格控制各信号层之间的距离,以防止信号间相互影响以及干扰,确保信号传输的稳定性。

阻抗匹配:在DDR总线下,各信号线需满足特定的阻抗要求,旨在降低信号回波及损耗,保障信号传输品质并增强系统稳定性。

差分走线设计:DDR总线常利用差分信号传输,此方式抗干扰性强且速度较快,科学的差分走线设计可显著提升系统的抵抗能力。

我在实践中的体会

在实际项目实施过程中,我充分理解并认识到DDR总线走线规则的关键性。曾因走线设计失误引发信号干扰问题,进而影响系统性能乃至出现故障。吸取教训后,我逐步累积了以下实践心得:

深入研读DDR规范:在设定DDR总线布线策略前,务必先全面阅读所选DDR内存的技术规格文档,掌握其布线准则及要求,以进行精准有效的设计。

科学布线:在设计电路板走线时,需严谨规划DDR总线走向,防范交错与过度弯曲现象,保障信号稳定传输。

确保信号完整性:在布线环节,务必严格监控信号完整性,维持差分信号的精确匹配和阻抗控制符合标准,以防止信号质量受损。

结语

总体而言,DDR总线布线规范对于确保系统的高效稳定运行至关重要。合理有效的线缆布局可显著提升系统运行的可靠性与效能。在实际应用过程中,我将持续积累经验,提升自身在DDR总线布线规范领域的设计水平,以期为项目的顺利推进尽绵薄之力。