身为一位电子工程领域的专业人士,我对DDR5设计及优化饶有兴致,这一议题对产品性能乃至整体系统效率稳定性皆具有深远影响。此文,旨在通过解析DDR5的物理特性、关键技术以及高效优化手段,以期为业内同行提供有益参考。

DDR5内存基本原理

首要之事,我们需明晰DDR5内存的构造及运行原则。作为现行主流DDR4的改良之作,DDR5内存首要改进则在工作电压与传输速率的提高上。较之DDR4的1.2V,DDR5内存选用了略微低的工作电压(常设為1.1V)。此外,其传输频率亦有大幅度更新,每根通信针可传输64字节数据,传输速度高达每秒6400兆字节。这一系列特性使DDR5内存在数据传输效率以及能耗控制上都取得了显著进步。

在具体实践中,DDR5内存设计需着重关注时序关系、数据线长度匹配以及信号完整性的问题。其中,时序关系是关键所在,需精准调控时钟、命令与数据信号间的时间关系,以保证数据传输的准确无误。此外,数据线长度匹配亦为重要考量,过长或过短均会对信号完整性造成负面影响,进而影响系统的稳定及性能表现。

DDR5设计要点

在筹划DDR5内存设计过程中,有四大要点需引起重视。首要的便是电源稳定性。该类内存对于电力供应要求较高,需保证稳定的电压与电流,以保障其正常运行。故而,在设计阶段,应精心规划电源供应电路,选用适宜的稳压器及电容,从而降低电压噪音与波动。

关键在于时序方案制定精准无误。DDR5内存架构对时序规则要求极高,必须完美控制信号传输节奏与次序,防止出现时序混淆及数据位置错乱现象。故而在设计过程中,需依据DDR5内存规格书所规定的时序标准,精心调整时钟、指令以及数据信号的传输时间,确保各信号间的时序关系无懈可击。

在此基础上,我们也必须关注信号完整性与抗干扰能力。由于DDR5内存在高速运转过程中容易遭受外部干扰,例如信号串扰以及反射现象等。为此,设计环节应通过架构良好的PCB布置、附加终端电阻及包覆屏蔽壳等方式来增强其信号完整性与抗干扰性能。

DDR5优化技巧

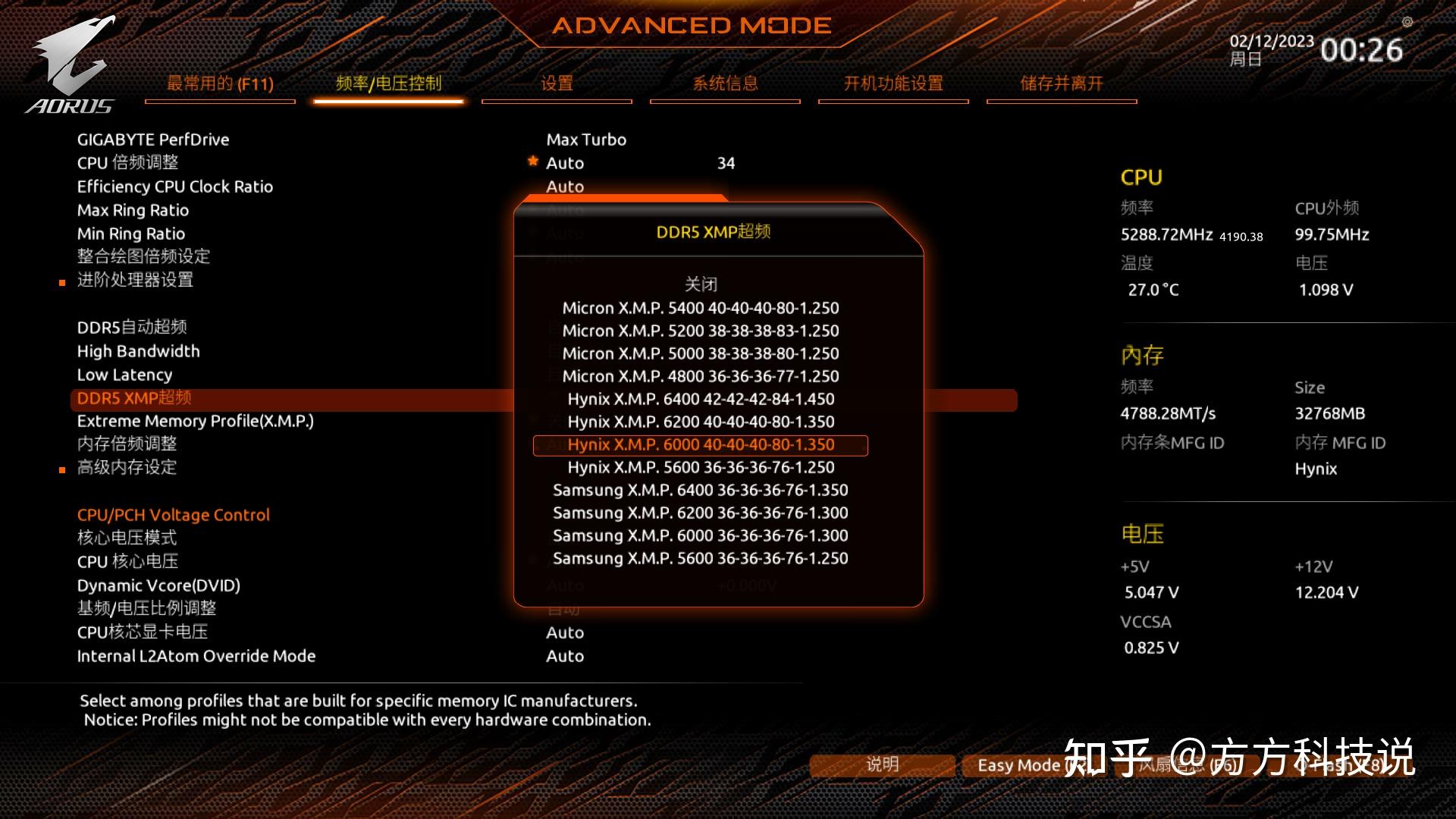

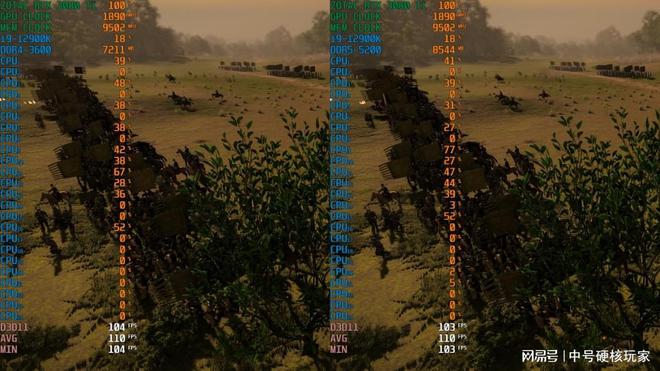

在进行电脑内存设计时,除了基本要素的把握之外,我们还需深度思考DDR5内存的优化策略。其中,首要任务便是时序管控。通过精细调节时序参数,如CAS延迟、预充电时间等,以提升DDR5内存的效能及耐用度。然而,时序优化并非一蹴而就,需通过全面的实测来逐步寻找最优解。

此外,通过调整DDR5内存布局也能明显提速。这包括优化PCB布局、缩短线路长度、加宽电源与地线宽度,以提升信号传输质量,确保系统稳定性及高效性。

采用高品质的DDR5内存颗粒与芯片组建则可显著提升系统效能。优良的内存物料具备卓越的稳定运行能力及较强的抗干扰性,从而增强系统性能及可靠性。

总结与展望

通过对DDR5设计及优化深度剖析,进一步洞察DDR5内存基础知识及设计关键点,同时掌握多项优化策略与方法。为今后DDR5内存设计,须关注时序把控、布局改良以及精选优质元件等关键环节,以提升系统整体效能及稳定性。

随着电子工程行业的持续发展,DDR5内存作为新一代内存标准,将在未来产品设计中扮演愈发关键的角色。面对日益复杂的系统设计难题,我们需持续学习并实践最新技术与方法。

我们致力于为业界工程师提供关于DDR5设计及优化的有价值信息,欢饮各位分享宝贵经验与独特见解,以期拓宽DDR5内存设计与优化的研究领域。