身为硬件设计领域的资深工程师,我一直关注着DDR3/4总线时序的重要性。在现代计算机体系中,DDR3及DDR4内存为主要的两种选择,总线时序的精确度直接关系到系统的运行效率以及稳定性。为此,我进行了深入研究并试图通过本文将所得经验分享给各位同仁。

DDR3/4总线时序概述

当今主流内存标准为DDR3及DDR4,二者虽存在某种共性但也具备各自特点。DDR3较之于前代DDR2总线时序更为精密,体现在频率的提升以及时序严格程度的加强。相较之下,DDR4则进一步提升了频率与带宽,对时序要求更为严谨。

在DDR3/4总线时序研究中,关键参数涵盖了时钟频率、时序延迟与时序关系等方面。科学配置并严格控制这些因素,有利于提升内存读写效率及稳定性,进而提升整个系统性能。然而,实现DDR3/4总线时序精确调控并非易事,需深刻了解内存控制器与内存芯片间的通信机制,精细调整时序参数,并实施全面的时序分析及仿真测试。

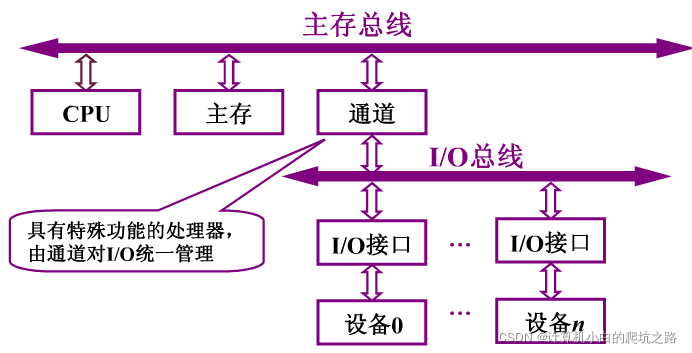

内存控制器与内存芯片的通信

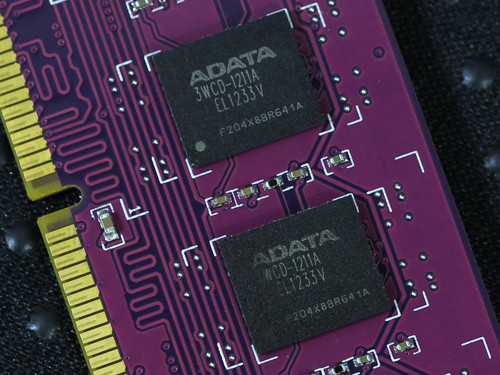

在DDR3/4系统中,内存控制器作为关键角色,操控着内存读写动作及其与内存芯片间的联络。其职责在于透过命令及调控信号引导内存芯片进行相应读写操作,并作好数据的传输准备工作。而内存芯片凭借这类信息作出反应,从而将数据传递至内存控制器内。

内存控制器和内存芯片间通讯依赖总线,而总线的稳定时序直接影响数据传递效率。设计内存控制器需关注时序设定如时钟频率及延迟等,同时还需调整各时序关系,保障通信顺畅,确保高速有效的数据传输。

时序参数的优化与调整

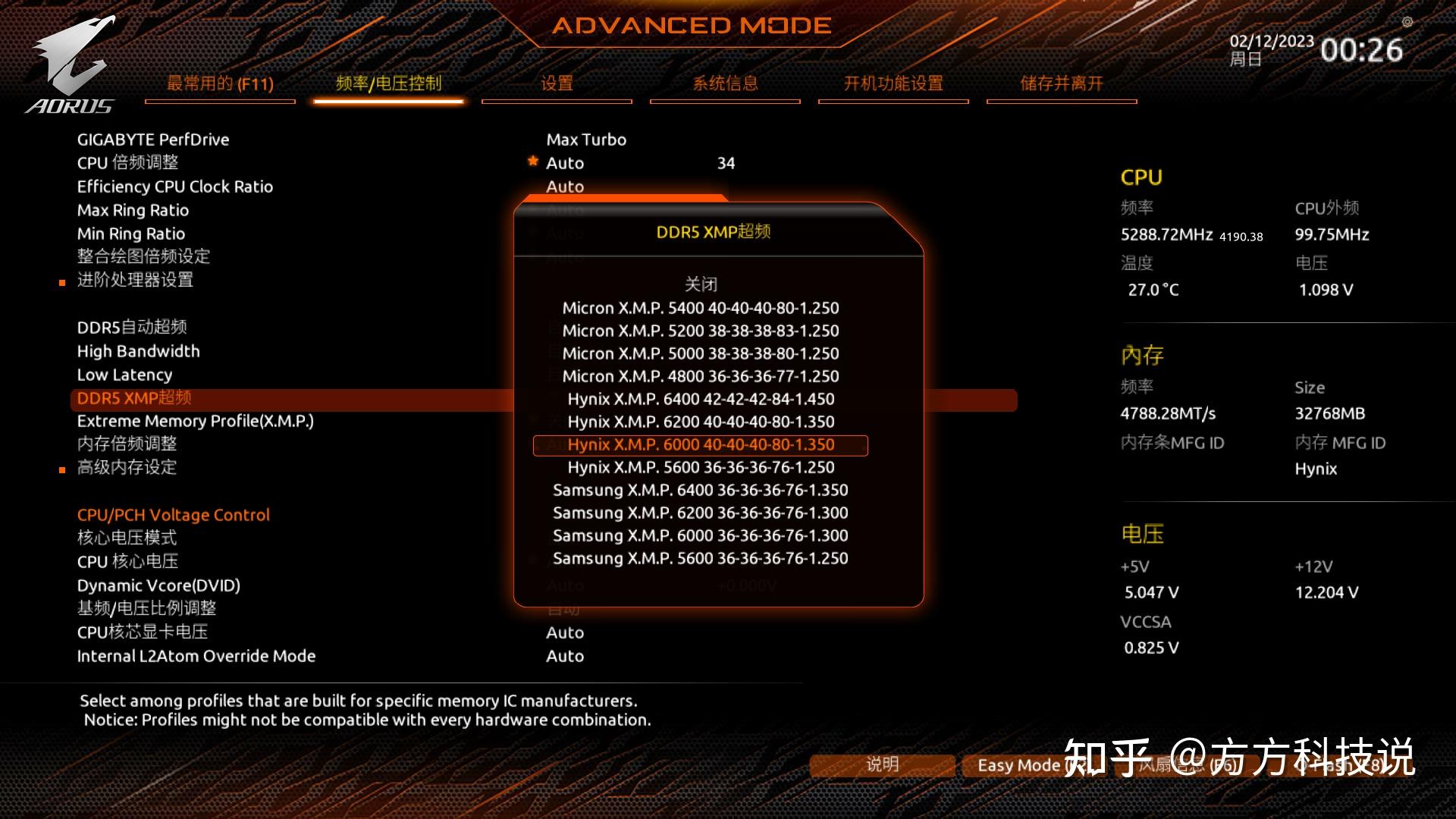

为使DDR3/4总线时序更具精确度与稳定性,应对时序参数予以优化及微调。其中,时钟频率作为关键参数,直接影响到内存读写速率。恰当调节此频率,可提升内存带宽并改善整体系统性能。

在时钟速率之外,时序延迟同样是影响总线时序稳定度的关键因素之一。为保障数据传输准确无误,内存控制器与内存颗粒间的通信过程需保持相应的延迟时间。针对特定的硬件环境及需求,务必合理设定此延时参数,从而确保通信的顺畅与稳定。

另外,调整时序关系是提升总线时序的重要环节。因各内存控制单元及存储芯片间存在差异化的时序需求,故需依据实际工况来微调,从而保障数据通讯的精确性与稳定性。

时序分析与仿真

为确保DDR3/4总线时序准确无误,需实施严格的时序分析与仿真。仿真技术可重现内存控制器与内存颗粒间的交互过程,评估时序参数配置是否达标,并识别潜在时序异常情况。

借助时序分析与仿真,工程师能够识别并妥善解决DDR3/4总线上的时序问题,保障系统运行的稳定高效。在此基础上,我们还需持续优化和调整时序参数,提高总线时序精度,从而提高内存读写效率。

总结与展望

深入研究与实践DDR3/4总线时序后,对内存控制和内存颗粒间通讯机制的理解更为深刻,并积累了丰富的总线时序优化经验。展望未来,会持续关注DDR3/4总线时序的发展方向,致力于创新优化策略及技术,从而进一步提升系统性能以及稳定性。

钻研DDR3/4总线时序的过程让我深深感到,此举极具挑战性且令人乐在其中。相信随着持续的深入研究与不懈摸索,对总线时序进行有效的优化必定能为未来计算机软硬件的发展拓宽无限可能。