近期,DDR3产品的EMI问题使我深陷泥潭。下方文章集结了我在困境中所秉持的观点和应对策略,期望能为同样遭遇此类困扰的读者提供启示。

什么是DDR3的EMI问题

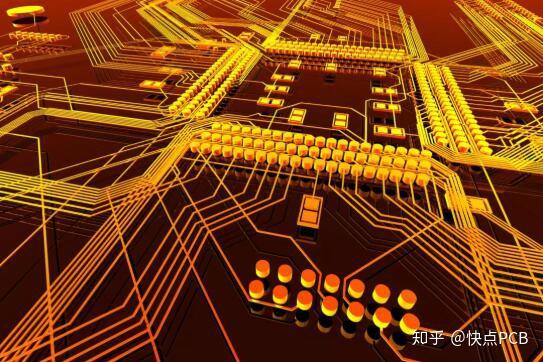

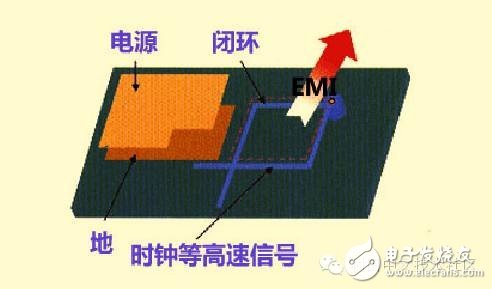

电磁干扰(EMI)是指电子设备操作期间对其他设备产生的电磁串扰现象,影响其正常运行。DDR3存在的EMI问题主要源自高频时钟和数据信号在印制电路板(PCB)上的传播引起的电磁干扰,从而显著影响了整体系统的稳健性以及效能发挥。

在深入研究DDR3EMI问题时,首要任务是理解其源头在于信号线上的反射、串扰和辐射等现象,这些都会破坏信号完整性,从而导致系统性能下降、稳定性受威胁甚至出现故障。为了妥善解决这一问题,我们需要全面考虑电路设计、PCB布局及电磁兼容性(EMC)测试各方面因素。

实际应用过程中,我发现DDR3EMI问题多发于PCB布局和线缆设计不足。由于DDR3接口运行频率高,信号稳定性至关重要,因此若布局或电路设计不当,EMI症状难免产生。为解决此问题,我对其进行了深度剖析并优化,以期消除DDR3的EMI困扰。

如何解决DDR3的EMI问题

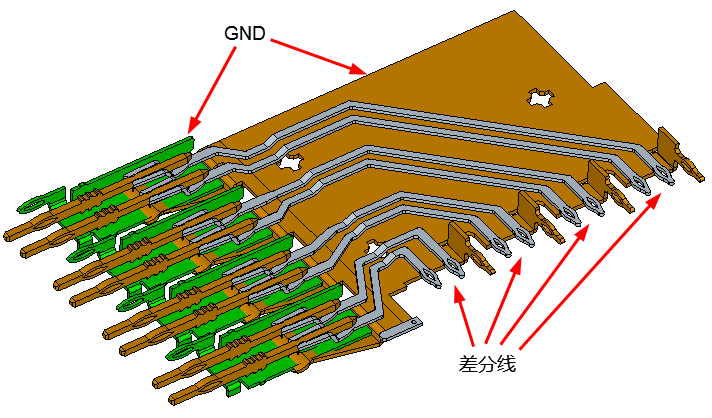

DDR3模块PCB布局要求严谨:需保证信号线长度适宜,避免产生反射和串扰现象;注重信号线与电源及地线间的隔离,以降低对外界电路的干扰;避免直角折弯信号线,推荐使用圆弧设计以削弱辐射影响。

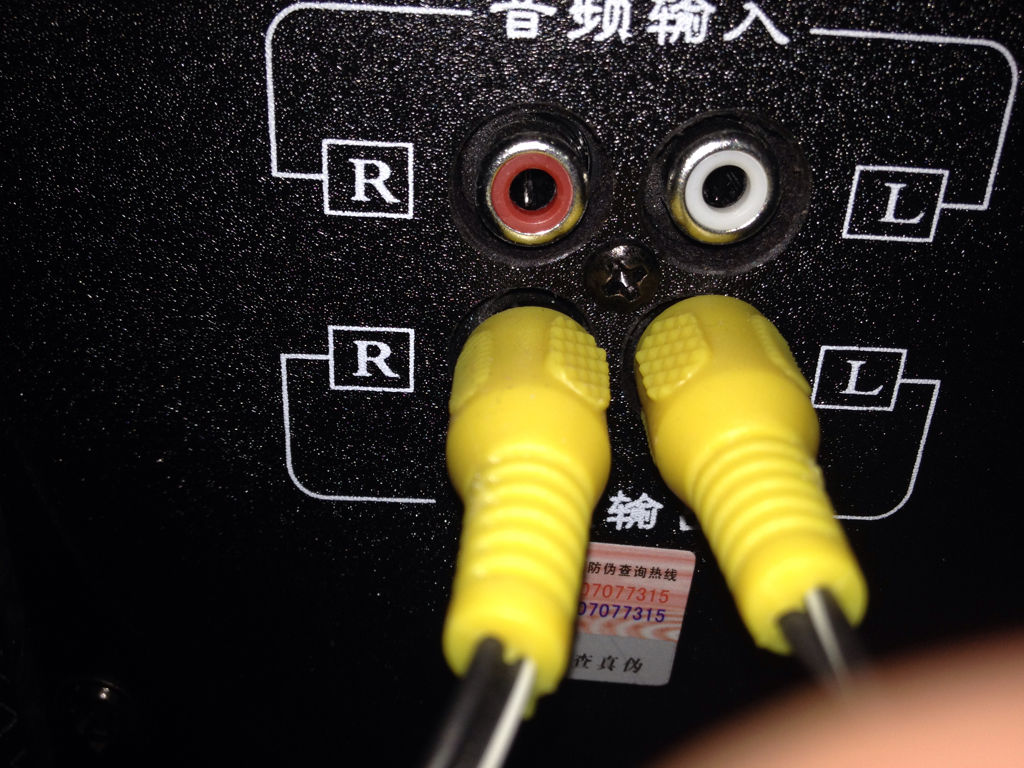

線路設計的精細:高品质的电缆对DDR3模塊性能具有关键作用。所以,选择合适的电缆材料与规格尤为关键。此外,应尽可能缩短电缆长度,避免信号传输延迟导致的失真。针对高频信号,建议使用屏蔽电缆以抵抗外部电磁干扰。

在设计阶段结束后,务必要对DDR3模组进行EMC测试,以保证其具备良好的电磁兼容性能。该项测试有助于发现并预防在模块运行过程中可能产生的电磁干扰,同时还可以衡量其是否符合相关标准。根据考量分析测试结果后,应该及时调整原有的设计方案,以排除潜在的EMI问题。

建议为DDR3组件的电源接入端口配备滤波器,消除电源线上的高频噪音和电磁干扰。依据实际情况与EMC测试结果选择恰当的滤波器,确保其能有效滤除噪声信号。

结语

通过深入剖析并实际操作DDR3EMI难题,我们现已掌握了有效的解决方法。其中,高效率的PCB布局,科学合理的线缆设计,全面完善的EMC测试及正确选择滤波器,被认为是解决DDR3EMI问题的关键因素。在未来的工作中,我们将不断学习新知识,总结经验,提升在电磁兼容领域的技术实力。

在工程学范畴内,严谨细致的研究与掌握至关重要,其对系统的正常运行及稳定性能有着直接影响。以DDR3存储器的EMI问题为例,我们需综合运用硬件设计、信号完整性和电磁兼容性等多个领域的知识,并结合实际操作获取丰富经验。在此,本人希望能借此机会分享个人经验,为大家提供参考,同时也期待各位同行共同探讨解决问题的策略和心得体会。