在深入讨论PS与PL端DDR速率交互前,有必要明确DDR速率概念。DDR,全称为DoubleDataRate,是反映存储器读取速度的指标,以MHz为单位的数值意味着其频率。在FPGA设计领域,精确掌握并优化DDR速率能高效提升系统性能以及节约能源。

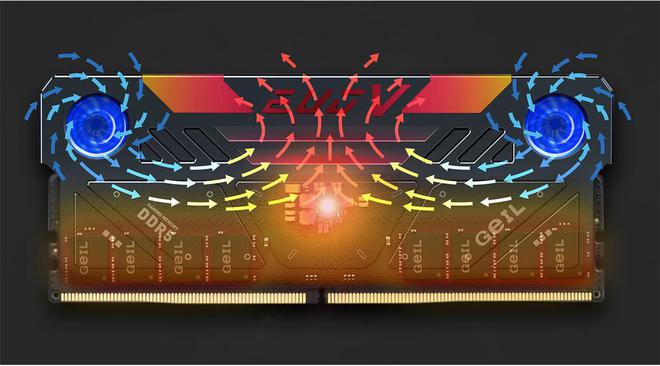

DDR速率直接影响着内存访问效率,对高速运算而言,提高DDR速率可缩短数据读取与写入时间,从而提升系统反应能力。而在PS设备访问PL展示出DDR的率数值时,需着重考量数据之稳定性、时节制及电磁干扰等关键性要素,属一项难度较高且至关重要的任务。

在FPGA设计过程中,提高PS读取PL端DDR的速度需具备多方面技能与经验,包括灵活运用技术以及丰富的实践经验。以下是本人对于提升PS读写PL端DDR速率的一些见解,希望能为有此需求的朋友提供参考。

PS读写PL端DDR速率的挑战

在FPGA设计中,PS与PL之间DDR速率的读取与写入乃关键要素,其中面临诸多困境需逐步化解。首先,必须严格遵循时序限制以保证高效稳定的数据传输;其次,精心调整与优化DDR控制器设置也为必经之路,依此方能洞悉DDR运作机制及时序需求。

另者,PS与PL间数据通道路径的设计亦是影响DDR运行速度的关键要素。优良的路径设计有助于降低信号传输延时,提高数据传输效率,进而提升DDR速度。然而,实践设计过程中,时常面临时序收敛难题及布线长度受限等挑战,故需在设计中寻求适当的权衡与优化策略。

此外,电子干扰与效能问题亦需在PS读取PL端DDR频率优化过程中得到重视。在高速传输数据过程中,电子干扰易引发信号变形及时序变动,从而对系统的稳定性构成威胁。同时,功耗的有效管理要求在提高DDR速度的同时,维持低能耗水平,使性能与耗能达到良好的均衡状态。

优化PS读写PL端DDR速率的方法

鉴于对PS读写PL端DDR速率的追求,有必要采用一系列高效的优化策略以实现系统性能的提升。首先,科学规划数据通道架构,缩短布线路径,降低信号传播延迟,从而显著提升DDR速度。此外,调整DDR控制器的各项配置参数(例如时序约束、时钟频率等)也能进一步增强系统的稳定性与性能表现。

针对电磁干扰及能耗问题,可采取相关策略以实现优化。例如,增加PCB上的地线与电源平面对抗电磁干扰;或者压缩信号线的长度,减少干扰现象。对于能耗管理方面,降低时钟频率、优化逻辑电路等手段均能有效降低系统能耗,提升整体性能。

在实际项目经历中,我曾面临PlayStation与PL端DDR速率优化的难题。经过反复试验及总结,我逐步累积了相关经验。在此过程中,我深感团队协作与知识共享的重要性,因为每个细微之处的改进都有可能对整个系统性能产生深远影响。因此,我坚信唯有持续学习与实践,方能有效应对此类挑战。

总结与展望

在FPGA设计中,优化PS读取PL端DDR的速率对于确保系统表现和稳定性起到了核心作用。通过提升这一速率,能加速系统反应、降低能源消耗及增强系统的可靠性。然而,要实现PS对PL端DDR读取速率的显著提升并不是一次性的工作,而是需持续学习与实践、团队间协作共进,方能获得长久胜利。

在职业生涯中,我会持续深化对PS读取PL端DDR速率优化策略的深度探索,以此丰富自身能力并实现技术与经验的更迭升级。我与期待与同样致力于FPGA研发事业的同仁们交流切磋,共襄盛举,为推动FPGA科技的发展助力添薪。