在双倍数据速率(DDR)领域,时钟(CLK)作为核心传递信号发挥决定性作用。然而,尽管身为非专业人士,我对CLK的具体含义与功能仍然感到困惑。因此,我决定深入剖析DDR中的CLK,探索其神秘面纱,旨在揭示这一难题的答案。

首先,请允许我深入探讨CLK在DDR中的明确含义。CLK,即Clock的简称,代表着时钟信号。那么,时钟信号在DDR的具体功能为何呢?通过深度研究后我发现,时钟信号在DDR中发挥着至关重要的同步与控制作用。其主要职责在于指示数据传输的精确时序,以保证数据能按正确顺序进行传输及处理。简而言之,CLK犹如一根指挥棒,主导着DDR系统的整体运作节奏。

CLK的频率对DDR有何影响?

DDR系统运作速率的核心要素为CLK频率。高频率提升了数据传输速度及系统效能,但同时也引发功耗增加与稳定性降低等问题。在设计DDR系统时,需考量两者间平衡,选取适宜的CLK频率以实现卓越的性能表现。

此外,CLK频率对DDR时序产生重要影响。各种DDR标准均设定了独特的时序规定,时序设置合理性直接关乎系统的稳定性及可靠性。因此,为保证系统正常运作,需参照DDR相关标准对CLK频率和时序进行精细调整。

DDR中的CLK如何与数据传输相关联?

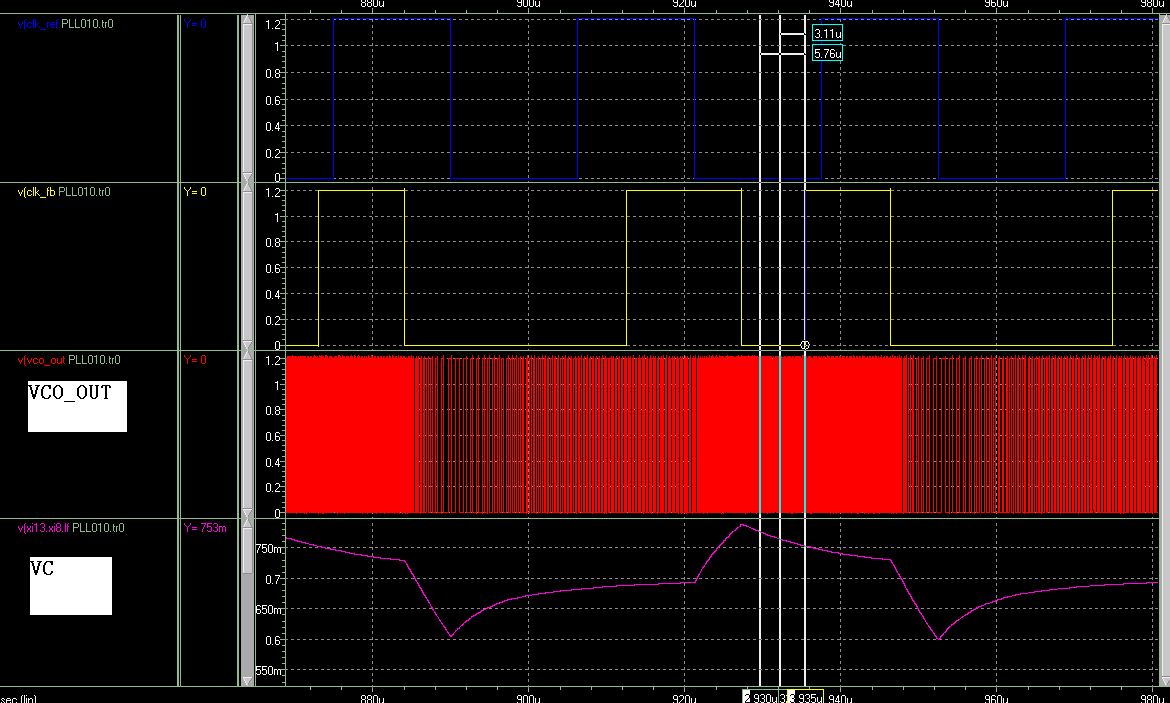

在DDR技术里,数据传送以时钟信号为基准,同步进行。通过特定的CLK边沿触发模式控制数据取样,其传输速率则受制于CLK的频率设定。因此,可以看出CLK与数据传输紧密相关。

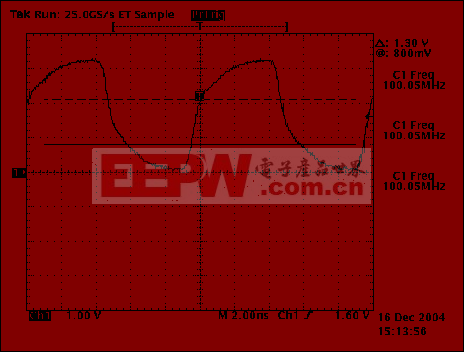

此外,DDR中的数据传输是双边沿触发式,每个时钟周期允许数据在上升沿与下降沿各传输一次,这极大提升了数据传输速率及系统反应速度。然而,CLK的频率与稳定度对双边沿传输可靠性有着直接影响,故在设计DDR系统过程中,需高度重视CLK信号质量及其时序控制。

时序控制是如何影响DDR中的CLK的?

时序调控在DDR系统设计中占据关键环节位置,涉及信号生成、分配及同步等领域。其表现优劣对系统功能和稳定运行构成直接影响。

在DDR体系架构下,时序控制需周全考虑诸多因素,包括时钟延迟、时钟偏差以及时钟抖动等。这些元素均可对CLK信号的质量及稳定性带来影响,从而波及整体系统性能。故此,设计DDR系统时,务必精细调整时序参数,以期确保时钟信号的精确、稳定传输与同步。

CLK在DDR中的应用有哪些特点?

在DDR体系结构中,CLK信号发挥着独特且重要的作用。它作为系统运作的主时钟,其稳定及精确度直接影响到整体系统性能。故而,在DDR设计过程中,必须高度关注CLK信号的质量及其时序控制。

其次,CLK信号的频率越高,系统性能越优,然而这亦伴随着挑战。高频CLK信号需消耗更多能量并对时间要求更为严格,故在实践应用中,必须权衡能耗与稳定性问题。

最终,CLK信号的传输率对数据传输效率与速度具有直接决定作用。在DDR系统内,通过精确调整及控制CLK信号的频率和时序特性,能够达到更高的数据传输效能,从而提升整个系统的运行效果。

结合实际案例看DDR中的CLK如何发挥作用?

为深入剖析DDR中时钟信号如何运作,我们选取了某公司研发高性能DDR内存的实例作详细解析。该公司追求内存的高速稳定读写表现。

在此案中,CLK信号发挥着关键作用。掌控其频率与时序参数后,该公司成功提升了内存条的数据传输速率,实现更卓越的性能。此外,其进一步优化了时序控制,保证CLK信号准确同步数据传输,从而增强了系统的稳定可靠性。

从本次研究中,我们深入领悟了CLK于DDR系统中的关键性地位。其既是数据交互的主导者,亦对系统整体性能产生举足轻重的影响。唯有深入理解并善用CLK信号,方能设计出高效稳定的DDR系统。

结语

深入剖析DDR中的CLK,使我对其角色及重要性有了更为深刻的理解。CLK不只是时钟信号,更是整个系统运作的关键要素。因此,在DDR系统的设计与运用过程中,我们必须高度关注CLK信号的品质以及时序调控,以保证系统能稳定且高效地运转。

敬请各位阐述,职业生涯或学术研究过程中,您是否遭遇相似的科技难关?又是怎样顺利应对的?欢迎畅谈分享经验与见解。