身为电子工程专家,本人对FPGA与DDR3的融合怀有浓厚兴趣及热情。数字化社会下,FPGA(现场可编程门阵列)凭借其强大的灵活性与卓越性能,广泛应用于各个领域;而DDR3(第三代双数据速率同步动态随机存取存储器)作为现代电子系统的关键存储部件,更是不可或缺。如何实现二者的高效连接,无疑是我工作中极富挑战且充满乐趣的环节。今日,特此分享我在此领域的研究历程及其感悟。

FPGA的基础知识

FPGA作为一种灵活可编程逻辑器件,使得硬件性能得以按需调整。在我日常的科研工作中,处理FPGA的过程宛如创建一个个微型世界。其核心部分为逻辑块阵列,借助编程技术,各逻辑模块可以胜任各类繁复的逻辑任务。于我而言,FPGA不仅仅是一台设备,更是一把探索未知可能性的利器。

DDR3存储器的重要性

DDR3存储具有高速的数据速率及宽广的带宽,因此已成为了现代电子装置中数据处理器的核心组件。在设计过程中,我始终注重提升DDR3性能,以满足系统对数据处理速度的严格要求。每次成功优化数据传输路径,都会带给我极大的成就感。DDR3犹如系统的心脏,持续为整体系统注入活力。

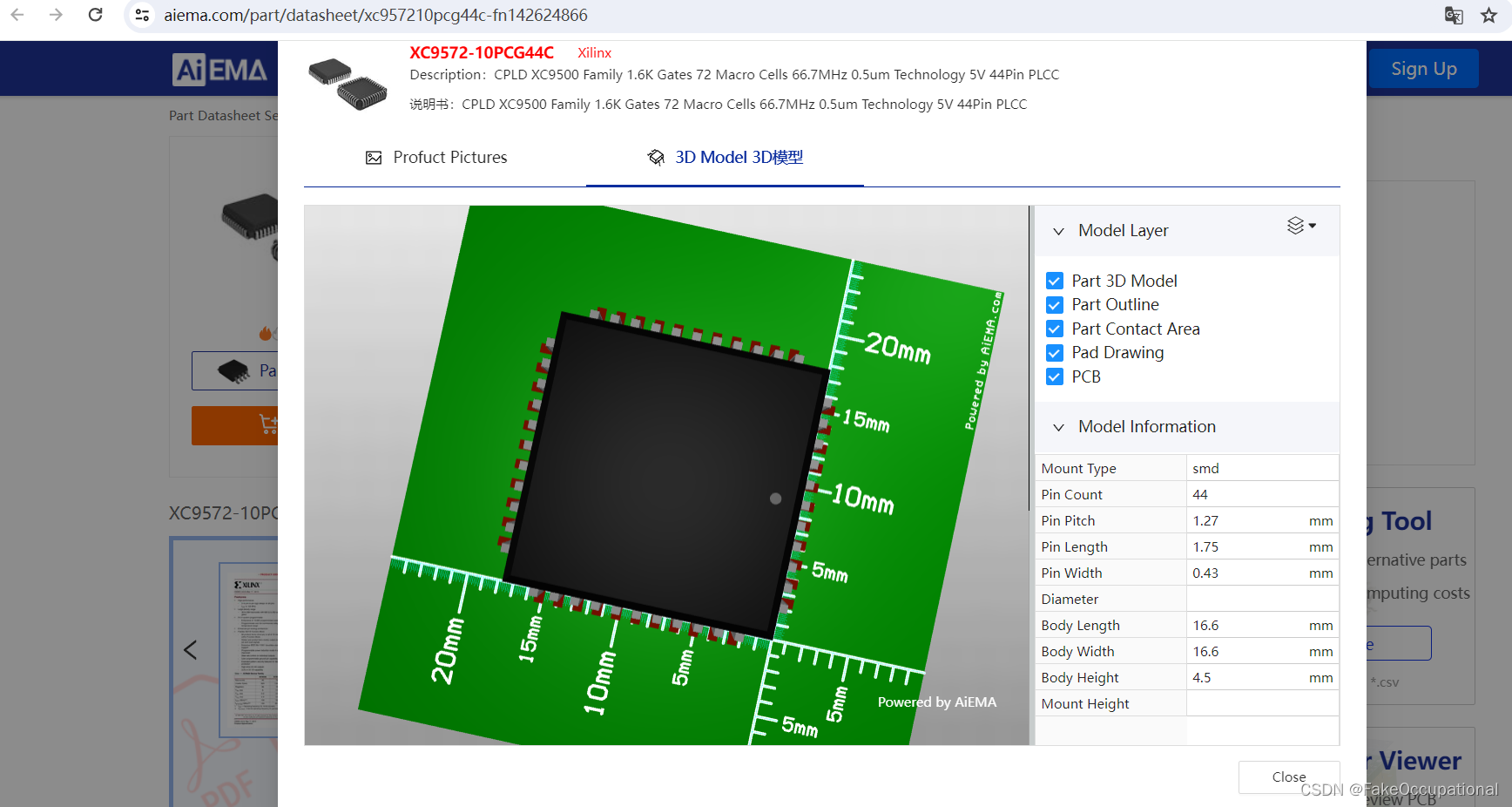

FPGA与DDR3的物理连接

在FPGA与DDR3的衔接环节,物理层设计为首要任务。我们需严格控制信号线布局以降低干扰,保障数据传输稳定性。在此过程中,任意线路的选择都直接影响着整体系统的平稳运作。

信号完整性分析

信号完整性的重要性不可忽视,尤其是在FPGA与DDR3的连接环节。实验中,为了探究信号的传输质量,我们频繁运用各类仿真工具。每一次参数调整,都是对细致入微的追求,对完美境界的探寻。而每次仿真成果的改善,都使我们更深切地理解到:精益求精,方能决胜千里。

时序约束的设计

在FPGA与DDR3的联接中,合适的时序限制是保障数据有效传输的核心要素。设计时需精确调控各项信号的时序,防止高速数据传输过程中的时序误差发生。此环节充分凸显了时间精准的重要性,微调毫秒之差都有可能对整体系统性能产生巨大影响。

电源和地线的布局

电源与地线设置对保证FPGA及DDR3设备稳定运行至关重要。在此过程中,笔者领悟到对电源管理的深入理解及其重要性,因其犹如为整体系统提供稳定能源供应。

调试与优化

在FPGA和DDR3联接成功之后,调试与优化成为至关重要的环节。在此阶段,我将借助多样化的测试方式以验证设计的准确性,并依据测试结果进行必要的调整优化。每次调试的顺利进行都令我倍感喜悦,每次优化都使得整体系统运行更为顺畅高效。

实际应用案例分析

在实践操作方面,FPGA与DDR3的结合颇具挑战性。我通过不同项目的历练,逐渐掌握了解决各类难题的策略。这些案例研究使我在知识层面得到充实,对于FPGA与DDR3的衔接也有了更为深入的认识。

未来发展趋势展望

伴随着科技持续进步,FPGA与DDR3的链接方法同样日新月异。作为这一领域发展的见证者和期待者,我深信未来新型材料及工艺的运用将会进一步提升其性能并增强稳定性。

个人感悟与成长

在深入研究FPGA与DDR3接口关联期间,我获取了丰富的科技知识,体验了独特的创新实践。面对挑战,我愈发坚强;收获成功,使我信心倍增。尽管未来仍有诸多未知,但我毫不畏惧,因为我对这份事业满怀热情,愿继续深入探索。

在结束本文之际,请允许我提问:在贵司的职责范围内,哪类挑战最能激发您的热情?敬请在评论区分享您的经验,与我们共同探讨,共同成长。期望本文能为您带来启示,同时感谢您的点赞及分享,以吸引更多志同道合者加入这场技术盛宴。