身为电子工程师,我热衷于探索DDR5显存封装尺寸的奥秘。此项技术不仅影响着数据处理效率,更是现代电子产品设计中的关键环节。本文将从工程师角度出发,分享我对DDR5显存封装尺寸的深度理解与感悟。

DDR5显存的技术背景

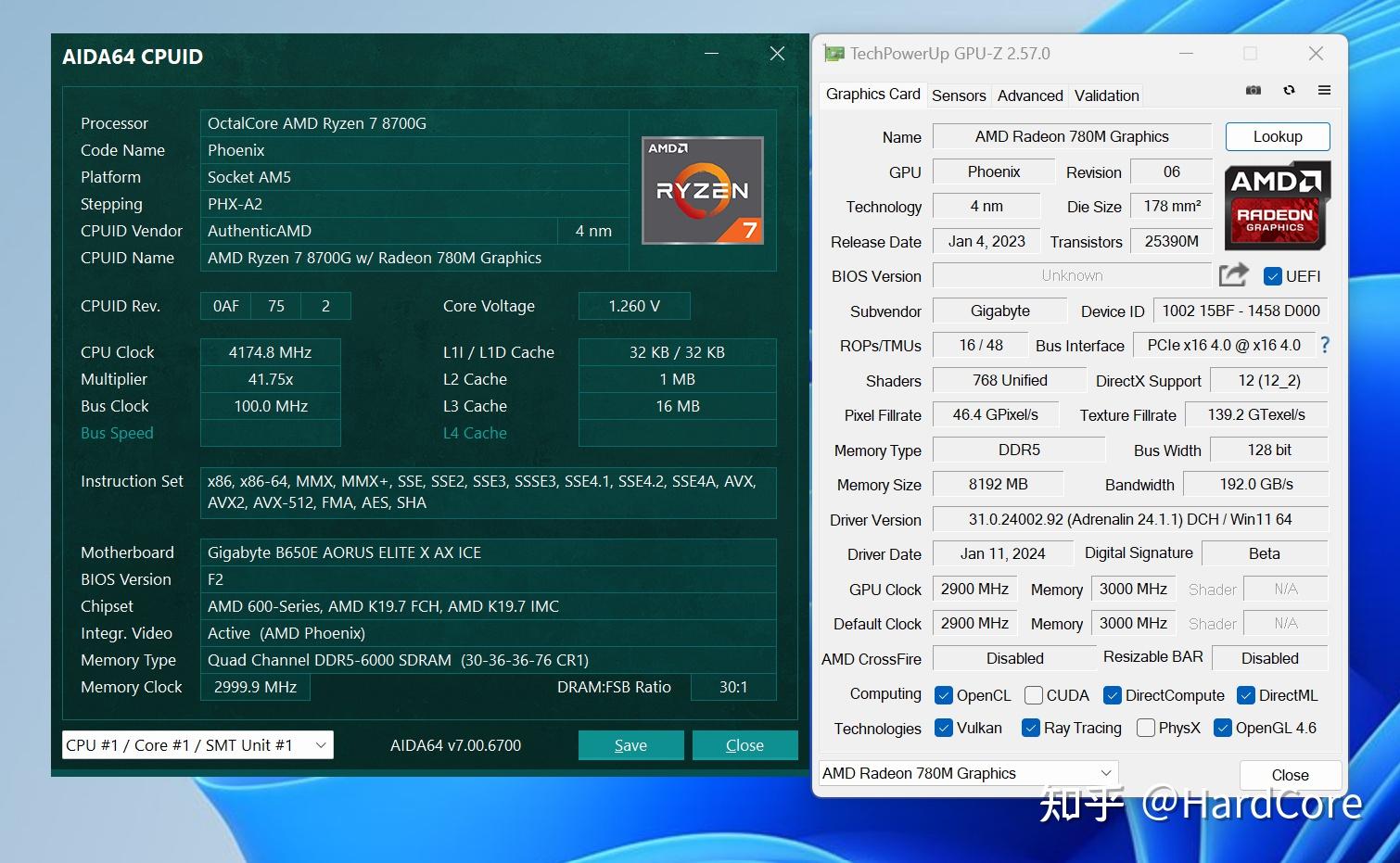

首先,让我们深入了解DDR5显存的科技脉络。作为第五代双数据率同步动态随机存取存储器,DDR5的诞生象征着内存技术的突破性发展。相较于前代的DDR4,DDR5在速度、电源管理及效率等方面有明显进步,这些改进对显存封装尺寸产生重大影响,使得产品更为紧密且高效。

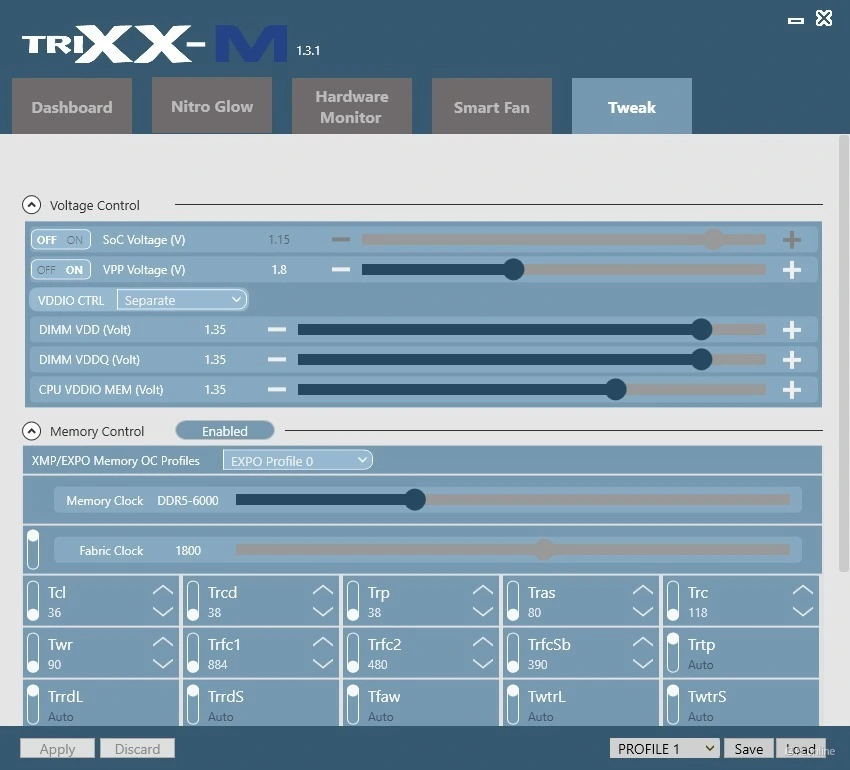

初次涉猎DDR5显存规格书时,复杂的数据与图表使我激动且疑惑。每项参数的调整均会牵扯到整体系统效能及稳定性。经过大量查阅与分析,我方才深入理解这些数值所代表的含义。

封装尺寸的重要性

接下来,我们将深入探讨封装尺寸对电子产品设计的重要性。封装尺寸直接影响产品体积、散热表现及最终用户体验。高度重视DDR5显存的封装尺寸设计尤为重要,旨在满足高效性能需求的前提下,避免增加额外空间负担或散热难题。

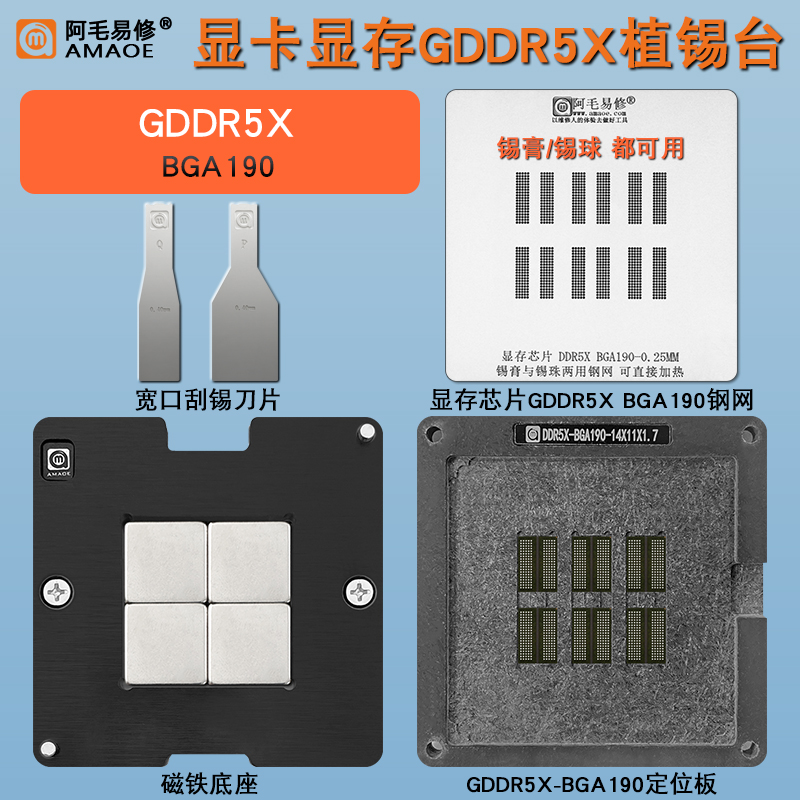

在方案初期阶段,需平衡众多需求,如在受限的电路板空间中优化元件布局,以及运用先进封装技术降低信号干扰等。此过程既富挑战性,亦要求我们对细微之处有严格把控与追求。

尺寸优化与散热管理

在DDR5显存封装设计中,尺寸调节和散热控制为两大要素。伴随着数据运算速率的提高,显存模块的能耗亦相应攀升,因此,更高效的散热策略势在必行。此外,为确保信号传输的高效率,封装尺寸的精细调整同样至关重要。

在处理高速数据传输与模块温度控制的难题中,我们团队经过反复研究和实践,最终采用创新性设计,成功实现了两者的平衡,使模块温度始终维持在理想状态。尽管这一过程充满曲折,但在攻克难关之后,那份油然而生的成就感让人难以言表。

实际应用中的挑战

在实践操作中,DDR5显存的贴片式封装设计需应对诸多挑战。譬如,在密集集成模式下,防止模块间的电磁干扰问题;在保障性能水准的前提下,设法降低制造成本等难题。

忆往昔某段时光,我方新产品遭遇量产前电磁兼容问题,为消此障碍,团队协同作战,连续数周展开高强度测试及调整。那时期日夜相伴于实验室,直至破茧成蝶寻得良策。

未来的发展趋势

展望未来,DDR5显存封装将会以更高的集成度及更优的能效比为主要发展趋势。在科技日新月异和市场需求日益增长的双重推动下,封装尺寸必定会持续朝着更为微型化、精密化的方向进化。

身为工程师,我对科技进步充满憧憬,坚信不断探索与革新能构建更强大且稳定的DDR5显存系统,助力电子产业蓬勃发展。

个人感悟与总结

回顾多年来对DDR5显存封装尺寸的探索与实践,深感技术与人文在此间交融。技术进步并非冷冰的数字与图表诠释,而是蕴含无数工程师辛劳与智慧的结晶。

在此过程中,我深入掌握了高效人际交往与协同合作的技巧。在解决技术难题之际,团队的鼎力支持和紧密协作成为克难制胜的关键因素。深感这种团队精神,使我对人类相互联系和理解推动社会进步的力量有更深刻的认识。

在此,恳请各位读者提出宝贵见解:科技进步推动下,我们应如何寻求人和技术之间的平衡点,以实现科技对全人类的恩赐?期待倾听您的高见,同时,也敬请您为本文点赞并分享,以便推动相关理念的传播与探讨。