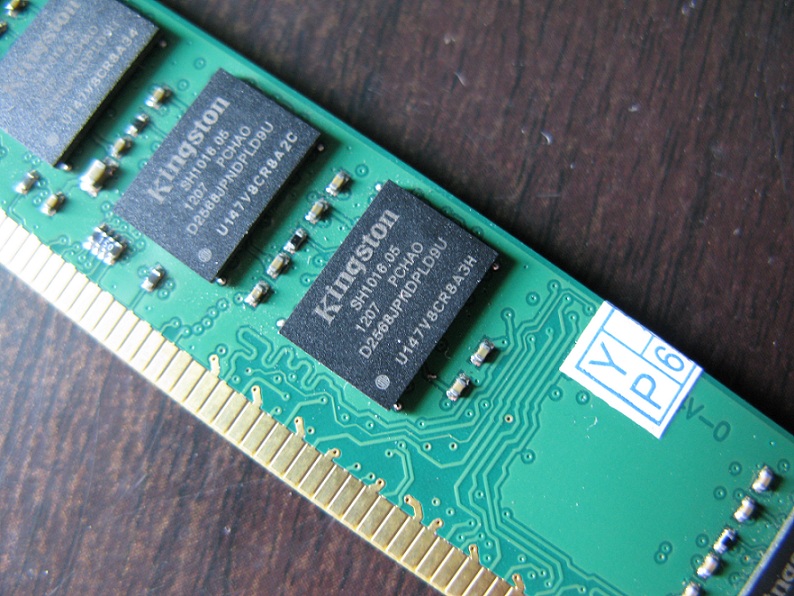

在当今数字化社会,无数电子设备环绕于我们周围,其核心便是隐藏其中的精密电路。身为电子工程师,我有幸深度探寻这复杂电路中的细微之处,探究看似平凡却至关重要的信号。今日,我愿与诸位分享DDR内存中那个决定成败的心跳信号——CLK。

CLK:什么是时钟信号?

计时信号,简称CLK,是数字电路中必不可少的节奏器,也是电子设备运转的基石。尤其在DDR(双倍资料速度)内存中,CLK信号的角色堪称关键。其决定了信息传递的速率,更会直击内存效能与稳态表现。每当CLK信号脉动起伏之际,恰似生命之心跳,驱动数据穿梭于电路之中。

初次邂逅DDR内存中的时钟信号,那是个炎炎夏日,内心涌现出无比好奇。经过多次严谨的实验与调适,终于领悟到CLK信号对于整个系统运行之关键。其不仅仅是数值象征,更是精确至纳秒级别的韵律,每一次跃动皆牵引全系统脉搏。

CLK的工作原理

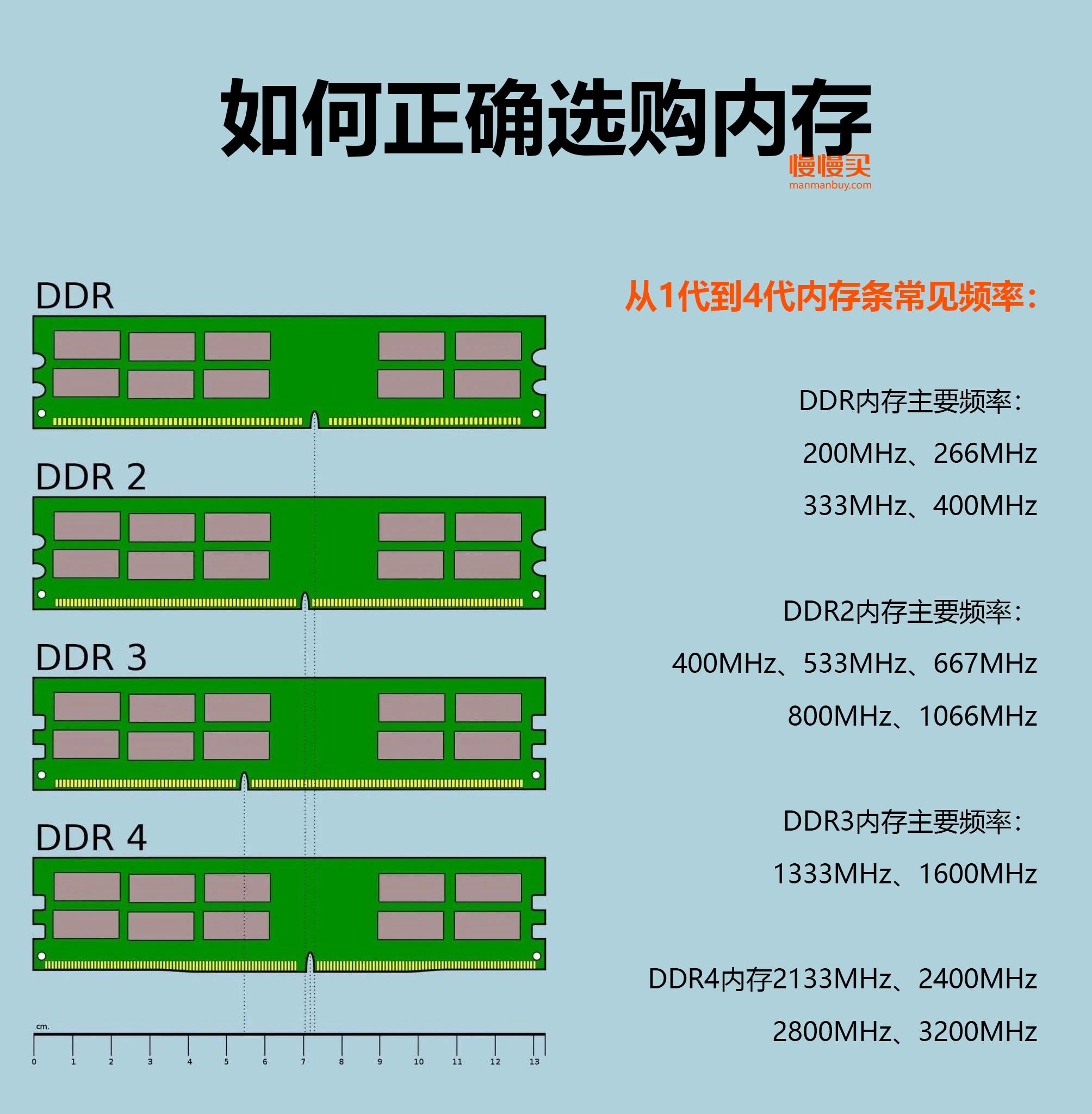

CLK信号由时钟发生器生成并以恒定频率持续发出脉冲。此脉冲即为电路各元器件行动的节奏指南,引导其按预定节奏运转。而在DDR内存领域,CLK信号每次的波峰及波谷均会引发数据的读取与写入动作。

依然记忆犹新的是,某次优化DDR存储器模块时,肩负起与CLK信号的持久博弈。逐一研讨其频率、周期及占空比,如同精良琴弦的微妙调整以寻觅最出色的旋律。尽管过程艰巨,但成功带来的效率提升和无比满足感难以言表。

CLK与数据传输

在DDR内存中,CLK信号既作为时间基准又充当数据传输纽带,它以双沿方式协助数据在内存与处理器间交互。正因如此,尽管基于相同的时钟频率,DDR内存仍能大幅度领先于传统SDR内存的传输速率。

曾在一项研发项目中,深切感受到时钟信号(CLK)在数据传输过程中所起的关键作用。我们的目标在于提高数据处理的速率,因此对CLK信号进行精细调节,以此增强数据传输的效益并明显缩短系统延迟。在此过程中,深入体验到电子工程的独特魅力,以及CLK信号在日常生活中的不可或缺。

CLK与系统稳定性

CLK信号的稳定性对系统稳定性有着重要影响。其微小的变动均有可能引发系统崩溃。因此,保证CLK信号的稳定是每位电子工程师的必备技能。

遇高速数据处理系统稳定性难题之际,深度挖掘故障原因,竟源于CLK信号波形出现异常。经精细调整时钟发生器参数后,系统得以恢复稳定运行。此事使我深感细节决定成败,微小信号亦可影响全局。

CLK的未来发展

伴随着科技飞速发展,DDR内存的速度亦随之不断攀升。每次频率升级均带来全新挑战,我们电子工程师需时刻学习并勇于创新,方能适应这股潮流。

对未来寄予厚望,我坚信新材料与新科技的运用必将使CLK信号愈发精炼且稳定。未来,数据传输将以雷霆万钧之势提升,消耗能源降低,计算力则越发强大,俱构筑于这个看似简单实则繁复精妙的CLK信号之上。

结语

历经深入研究DDR内存中的CLK信号后,我不仅积累了丰富的专业知识,更是对电子工程之美有了更深的体悟。CLK信号犹如数字世界的脉搏,每一次跃动,都代表着我们对未知的无限向往。

在此,请问各位,你们对电子设备中时钟信号有何深见?请留下宝贵评论与我们共同展望未来无限可能!