自首次接触计算机硬件至今,对内存配置始终保持浓厚的研究兴趣。特别是DDR4内存的时序延迟,它影响着系统性能,也成为了我深入探索科技奥秘的桥梁。今日,愿与各位共享在此方面的经验心得,望能为同好者提供参考。

初识DDR4内存时序延迟

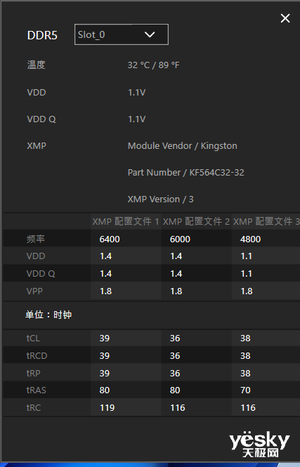

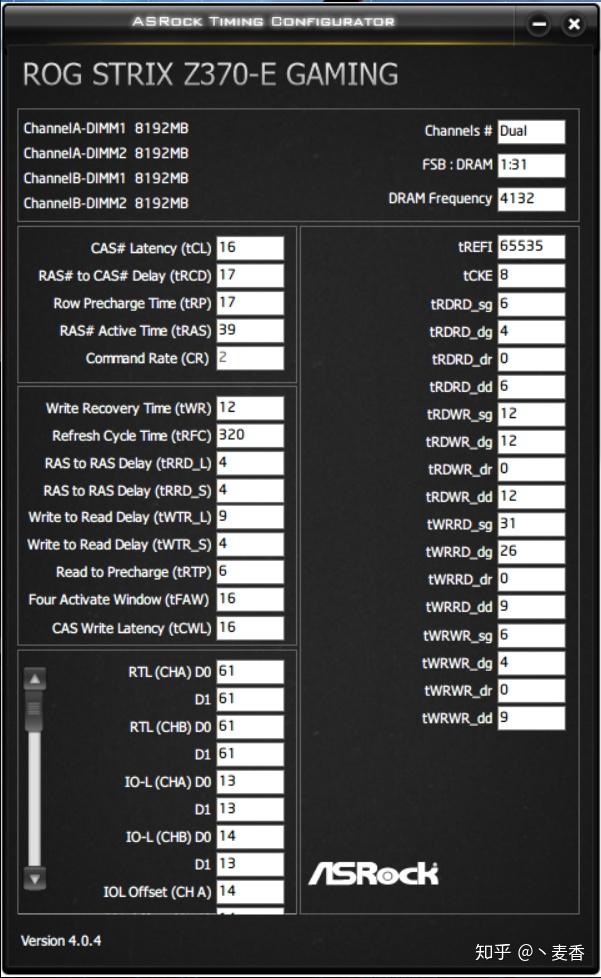

初次接触DDR4内存的时序延迟,我深感其深远含义和复杂性,使我既充满期待,也困扰不解。实际上,理解这个领域需要深入且持续的探索与实践。简言之,时序延迟就是内存模块完成数据请求所需的时间,由众多重要因素构成,例如CL(CAS延迟)、tRCD(RAS至CAS延迟)、tRP(预充能延迟)及tRAS(行激活周期)等等。每种元素均会直接影响内存的整体性能表现。

CL(CAS延迟)的影响

CAS延迟,作为内存时序的重要参数,常常被研究者关注。通过一次实验,我们发现了降低CL值能够缩短内存响应时间,进而提高处理效率。然而,这并非线性关系,过度降低可能引发系统不稳定。因此,在设定CL值时需谨慎权衡性能与稳定性。

tRCD与tRP的微妙关系

在电脑内存时序设置中,tRCD(RAS至CAS延迟)及tRP(预充电延迟)至关重要。通过深入分析二者间的微妙联系,可进行适度调整以优化存储器访问效率,确保系统稳定且提升实际操作性能。而此过程需审慎周全并具备高度的洞察力,因每一次成功的优化成果皆能带来极大的成就感。

tRAS的调整策略

tRAS(内存行为周期)是指内存行开放至关闭所需最短时间。研究表明,该环节对内存稳定及性能均具有显著影响力。适度调整tRAS可防止内存耗电过载及产生过量热量,尤其适用于长期运行环境。依据实际应用与内存配置,精细调整tRAS参数,方能实现系统最大化性能。

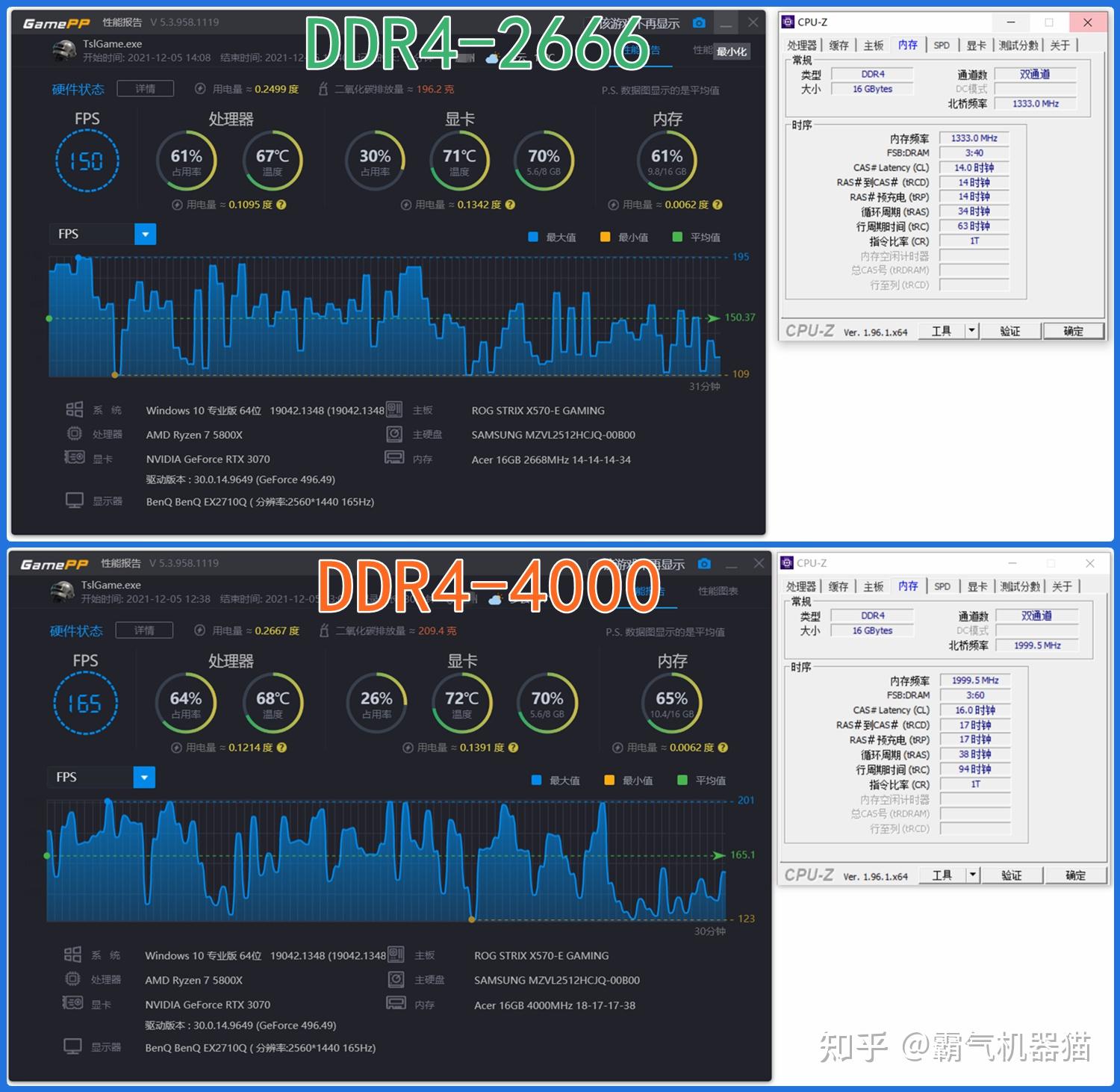

超频与时序延迟的权衡

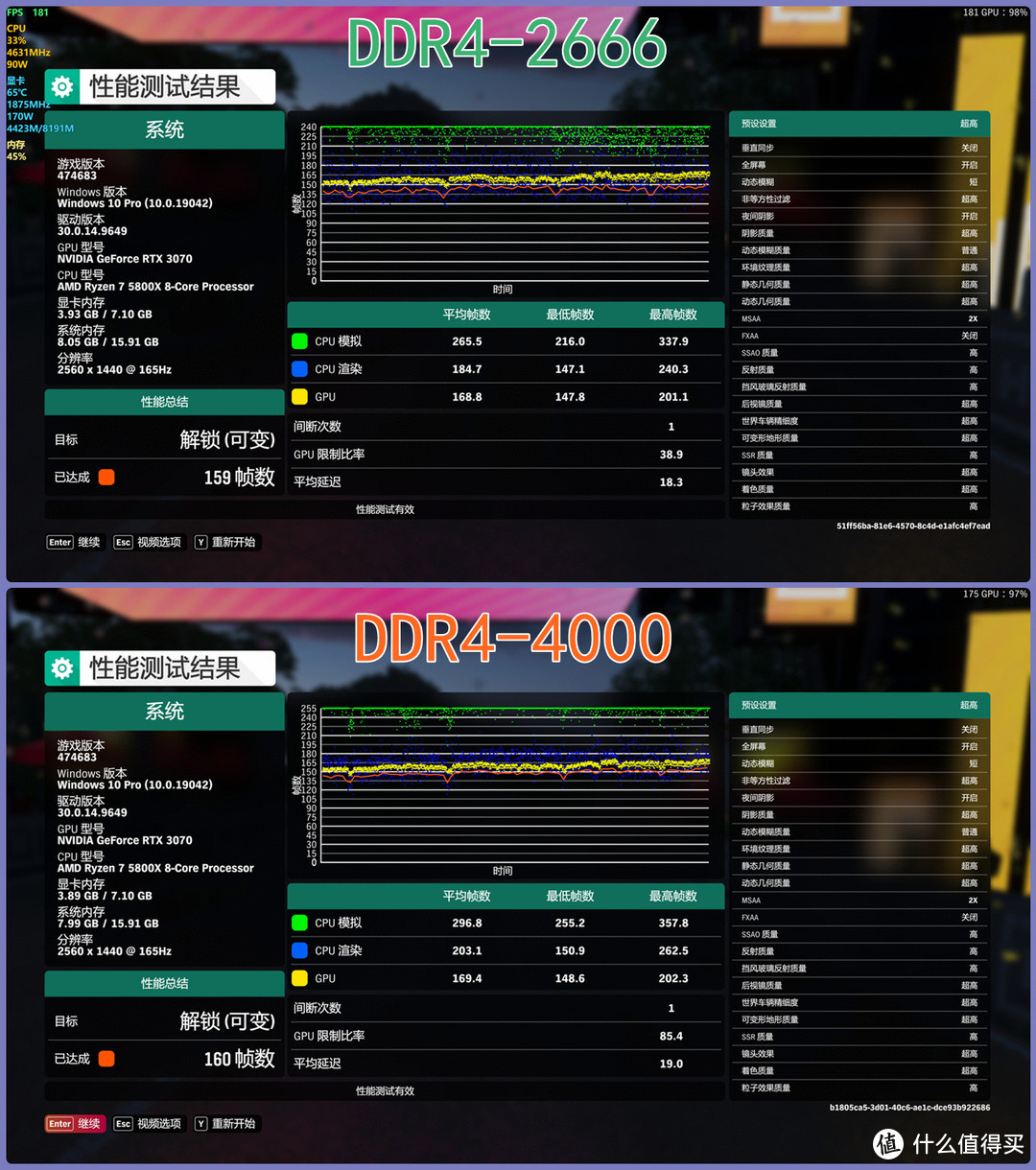

身为一名硬件玩家,超频自然是我所热爱的话题之一。但是,超频过程中需要追求频率提高和时序稳定之间的微妙平衡。经历数次探索,我已经掌握了如何在实现超频的同时保持良好的时序延迟,这既是对我技术水平的极大检验,也是对我耐心的磨炼。

实战经验分享

长期的硬件调试与优化经历,使我掌握了多元化的实操技能。比如,依据具体应用环境调整时序延迟策略:在追求计算机顶级性能的游戏和高性能计算中,我会降低时序延迟;而在普通办公及轻度应用的环境中,我会优先保障内存的稳定有效性。这些实践的累积,使我更为深入地认识到DDR4内存时序延迟的关键性与复杂性。

未来展望

随着科技持续精进,DDR4内存标准亦日臻完善。未来,我们期待能有更具创新性的内存技术诞生,以期实现更低的时序延迟与更高的性能表现。身为一位硬件发烧友,我将持续关注此领域动态,分享我所得之最新见解。

总结与反思

在个人探索中,我对于DDR4内存延迟有了深入理解。此过程不仅使我学习并掌握了大量的计算机硬件知识,同时也深刻体验到了科技的无穷魅力。每次的调整与优化都对自身的技术水平及耐心提出了挑战。期望我的经验分享能为正处于或即将开始这段旅程的朋友提供有益参考。

纵观计算机系统的使用而言,您在选择内存时,最为重视其何种特性呢?是速度、稳定性,抑或是耐久度?敬请在评论区分享您的见解,共同探讨与学习。若认为此文对您有所裨益,别忘了点赞并分享给他人。