在此论述中,身为电子工程师的我,将分享个人应对DDR3数据线误差所积累的经验与洞见。电子学上微乎其微的误差,极易引发严重后果,特别是在高速度的DDR3内存系统中。此文将深入探讨相关议题,以期提供同行有益的观点,推动更深度的技术交流。

一、初识DDR3数据线误差的挑战

身为资深电子工程师,首次遭遇DDR3数据线误区乃在某项目之中。彼时,系统数据传输频发失误,严重影响产品稳定性与性能。对此困境,我深知责任重大,此非仅为技术难题,更涉及企业声誉及客户满意度。

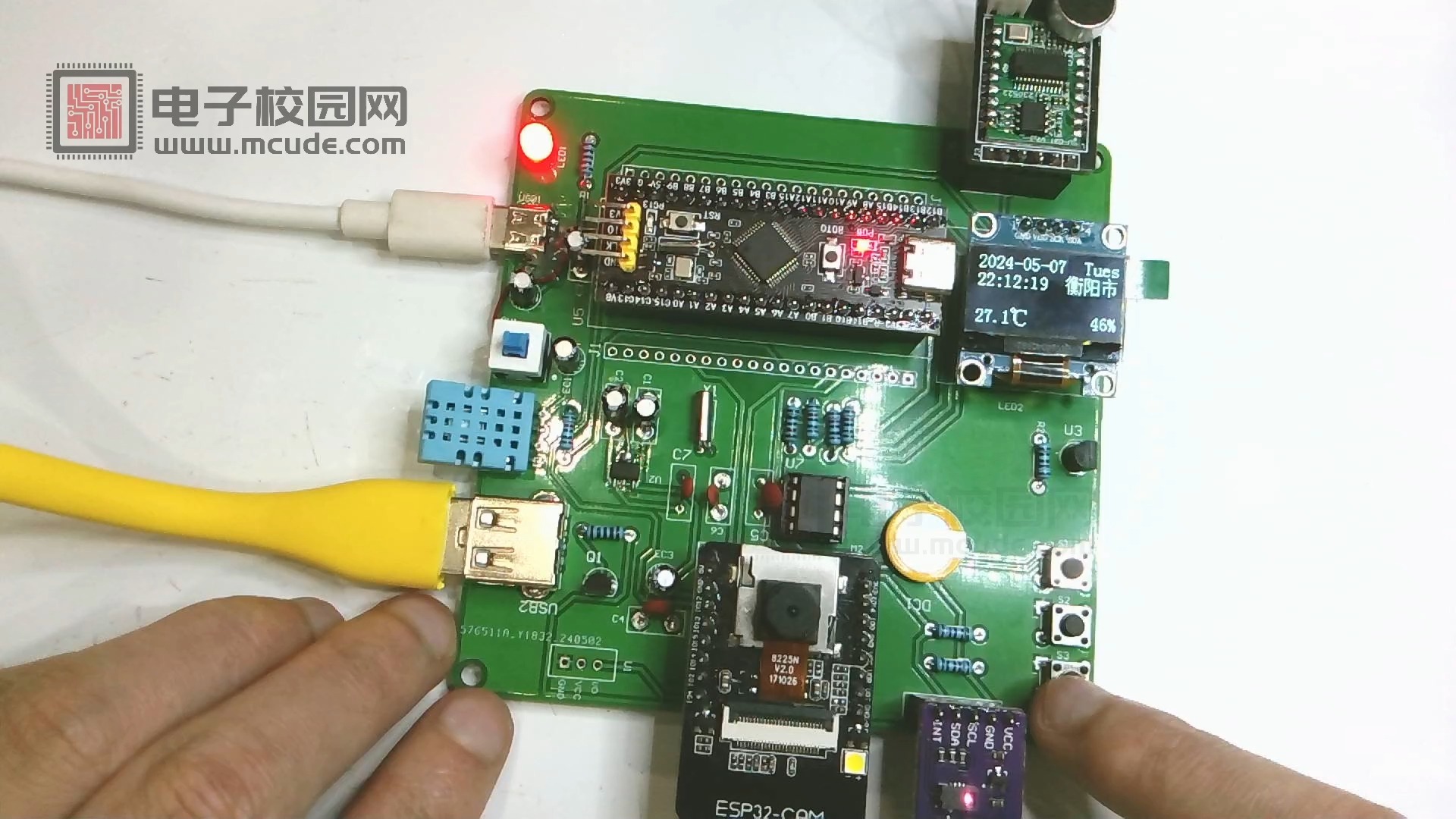

深入剖析之下,发现DDR3数据线误差缘由极其复杂,涉及信号质量、电源稳固及路线规划等诸多因素。基于此,我们对现有设计与测验程序进行全面审查,期望寻觅解决之道。

二、深入信号完整性的探索

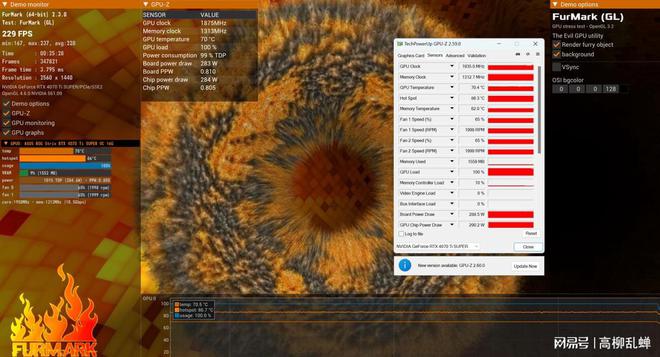

为改善DDR3数据线误差问题,首重信号完整性研究。借助高速示波器及专业软件,对数据线上信号进行深度剖析。结果显示,信号上升与下降沿存在显著抖动,此乃误码之主因。

为提升信号性能,我们对线路的阻抗搭配与终端配置进行校正,同时优化PCB层级设计及走线布局。尽管这些措施显著增强信号稳健性,但问题尚未彻底解决。此番经历突出显示,解决DDR3数据线误差需采用全方位、系统性的策略。

三、电源稳定性的关键作用

在信号完整性调试没有明显效果后,我们发现电源稳定性也会对DDR3数据线造成干扰,从而引发误差。于是,我们优化了电源设计,增设了去耦电容与电压调节器,旨在提升电源的纯净度与稳定性。

经过精细调整后,本系统的稳定性能得到显著提升。但需注意的是,电力管理乃一长期且复杂的任务,需要实时监控与优化,以便适应各类运行环境及负荷状况的转变。

四、线路布局的优化实践

除信号完整性及电源稳定两大关键因素之外,线路布局亦是影响DDR3数据线误差的重要环节。因此,我着手重新审视并优化我们的PCB布局,尤其关注数据线与控制线的布设方式。通过采用差分对走线、控制线间距以及走线长度匹配等策略,有效降低了信号间的串扰与反射现象。

此套设计策略的实施,既提升了数据传递精度,亦优化了整体性能。然而,我深知,技术日新月异,线路设计改进是个无尽过程。

五、测试与验证的重要性

经过诸多精细化优化后,我深刻认识到测试、验证之于工程的关键重要性——唯有通过严谨的测试,才能保证设计的高效性以及稳健可靠。为此,我创立了一整套涵盖功能、压力及环境三方面的全方位测试方案。

通过实践测试,可即时揭示潜在风险点与问题所在,从而有针对性地施行改良措施。尽管耗费时间精力,然而却成为保证产品卓越品质的必由之径。

六、团队协作与知识共享

在致力于消除DDR3数据线误差问题的过程中,我深感团队合作的重要价值。团队成员的专业技能与经验构成了宝贵资源,借助高效沟通与协同,能够快速寻得问题的解决之道。

我积极推动知识共享理念,倡导团队成员共同交流研究心得与观点。这种交流方式既有助于问题的尽快解决,同时也推动了全队的技术实力提升。

七、持续学习与技术更新

在应对DDR3线路误差技术难题之际,深感持续学习与技术创新的必要性。面对信息产业的变迁与发展,关注技术领域的最新动态与理论,方能维持竞争优势。

故而,我选择定期参加业界研讨会,研读前沿研究文献,乃至修习线上课程。通过这些努力,使我对DDR3数据线误差有更深的认识并拓展了解决方案的视野。

八、从误差中学习,迎接未来的挑战

DDR3数据线误差带来困扰之际,也是锻炼和提升自身的好时机。通过直面这一难题,技术水平得以提升,解决复杂问题的自信也显露无遗。

科技发达下一时代,面对诸多新挑战是必然趋势。我坚信,只要怀揣好奇与热忱去不断学习,必定能够战胜任何难关。

总览:于DDR3数据线误差事件处理中,我历经验证、寻求规律,终能寻获解答之道。此次经历使我领悟至深:每项技术难关皆为激发个人成长之契机。愿此经历与领悟,能启迪同仁,共同探讨技术探索之奥秘。

在此,我愿就此问题征询各位读者:在日常工作中,曾遭遇过哪些难以逾越的技术难题?您又是怎样应对与解决的呢?欢迎您踊跃参与交流,文章分享与点赞更将助力于推广此类经验至更广泛的行业群体。