身为电子工程专家,对于DDR(双重速率同步动态随机存储器)在当前计算机体系结构的关键地位有着深刻理解。今日,愿与诸位探讨有关DDR内存引脚定义的议题。这看似平淡无奇的主题背后,正是科技进步及标准制定的鲜活实例。

DDR内存的历史沿革

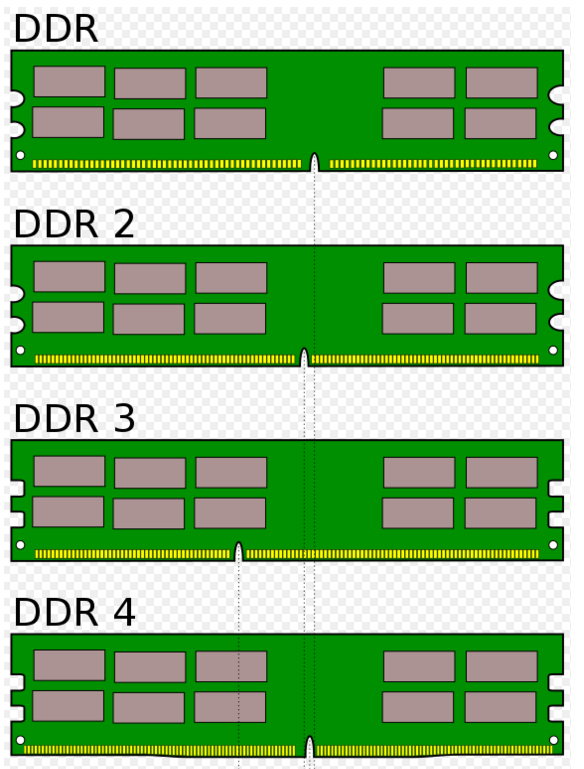

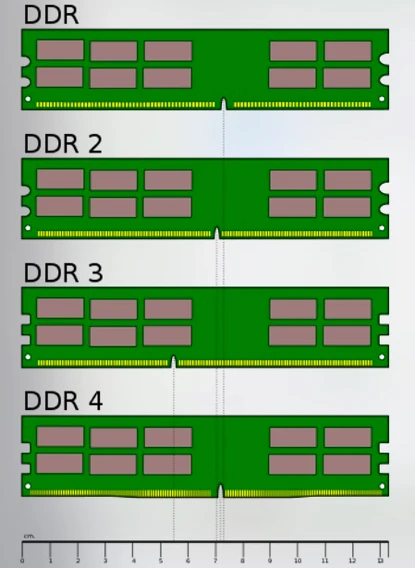

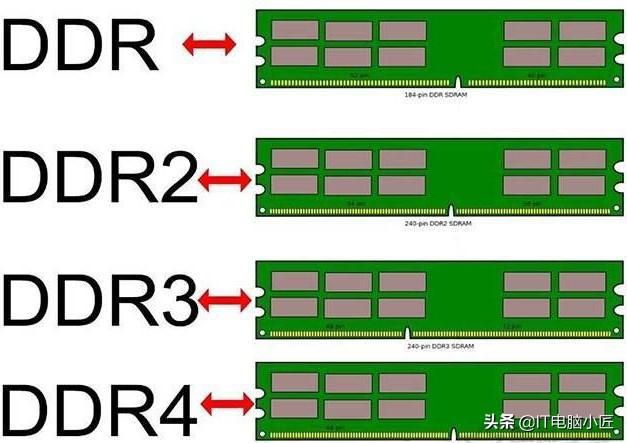

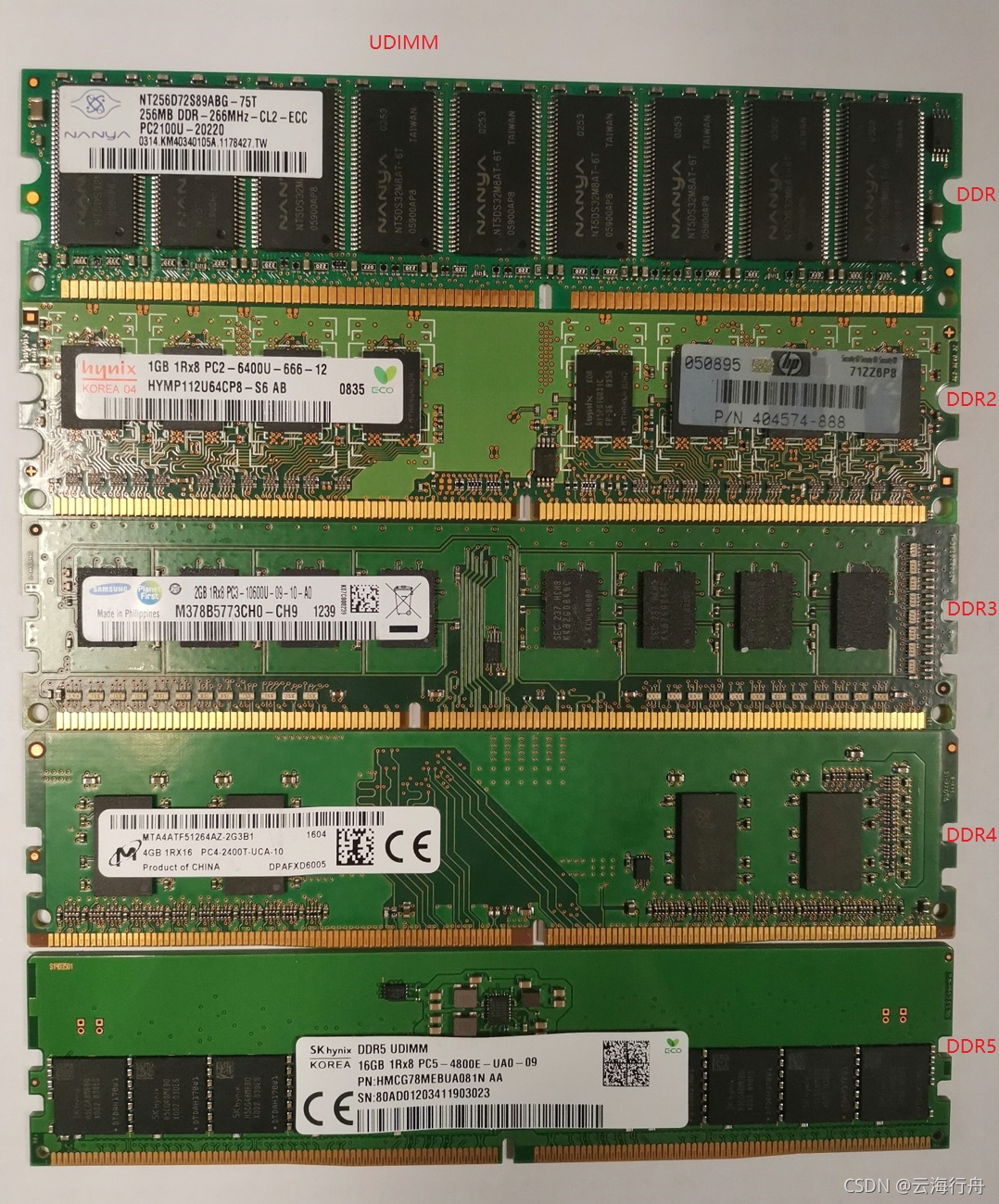

初次的电子工程学习中,DDR内存对我来说颇具新意。当时,我对其理解只停留在比传统的SDR(单数据率)内存更快且效率更高。然而,随着学习深入,我逐渐明白DDR内存的发展并非仅仅是速度的提升,更是一种技术与标准共同演进的过程。自DDR到DDR2、DDR3,直至如今的DDR4以及未来的DDR5,每一步的跃升,都是引脚定义相应调整的结果,以此来应对日益提高的数据传输速率及更为复杂的电源管理需求。

引脚定义的重要性

无论对于DDR内存的普及还是其兼容性来说,引脚定义的标准化都是关键所在。身为一位工程师,我深感在电路板设计过程中,精准的引脚定义乃是确保内存条正确安装及正常运行之基石。每一根引脚的功能、位置与电特性皆需严格遵循业界规范,从而保障各厂商间内存条与主板的互通性得以实现。

DDR内存引脚的标准化进程

在DDR内存技术演进的道路上,JEDEC(电子工程设计发展联合会)起到了举足轻重的作用。身为全球半导体行业规格设定者,JEDEC制订了严谨的DDR内存引脚定义标准。此标准涵盖了引脚数量与布局,以及信号电气特性,如电压水平、时序参数等方面。身为工程师,我常查阅JEDEC的规范文件,以确保我的设计遵循业界标准。

引脚定义的技术挑战

伴随DDR内存技术的快速进步,其引脚定义亦需应对新技术挑战。如数据传输速度提升所引发的信号完整性问题,以及电磁干扰(EMI)与串扰等在引脚布局及布线设计中的处理均至关重要。身为工程师,在设计过程中须充分考虑上述因素,以确保内存系统的稳定可靠运行。

DDR5时代的引脚革新

随着DDR5内存技术的推出,其引脚定义上的创新再次引起关注。DDR5内存凭借更高的数据传输速率以及尖端的电源管理技术,使得引脚定义得到相应完善。身为一名职业工程师,我对DDR5的新特性充满期待,但也深知这将给我的工作带来新的挑战。

工程师视角下的引脚设计

在我的日常工作中,引脚设计需精准而繁琐。每个引脚的布局及功能均须严格规划,以保障内存条稳健运行。我常需协同团队成员,共解设计之难题,从而保证公司产品契合客户需求。

引脚定义与系统兼容性

电子行业中,系统兼容问题始终如一。尤其是DDR内存引脚规范对其与主板兼容性的影响不可忽视。身为一名严谨的工程师,深知引脚细节的稍有偏差都可能引发系统的不匹配。故而,在设计过程中,我会严格遵循业界最新标准,以保证产品的高质量和稳定性。

未来展望:DDR内存的引脚将如何演变

展望未来,DDR内存的引脚定义将随科技进步持续演进。身为工程师,我对此满怀憧憬。坚信新材料与新工艺的运用,将助力DDR内存在性能及能效方面取得重大突破。然而,我亦深知这将引发对引脚定义的全新挑战并需进行相应调整。