自涉足电子工程领域,DDR4内存中的DQS信号始终令我备受关注。在此与诸位分享个人对其的认知与感悟,希对对此领域深感兴趣者有所裨益。

DDR4内存的基础知识

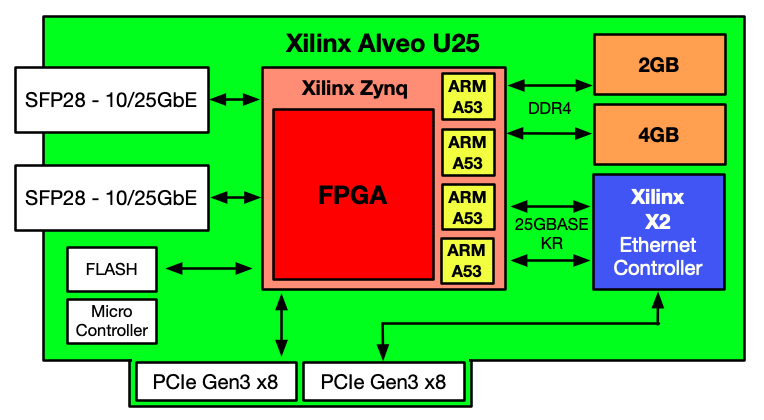

DDR4,第四代双倍数据率同步动态随机存取存储器,现已普遍应用于个人电脑及各种电子设备中。较之DDR3,DDR4具备更高的传输速度以及更低的能耗。其中,DQS(数据选通信号)起到了关键作用,它负责对数据信号进行校准以保证读取写入过程中数据的精准无误且稳定可靠。

深入学习过程中,逐渐理解到DQS信号并非单纯技术性概念,其犹如内存通信中的"导向器",精准引导数据流向。每一次对信号运行机理的探索,都让人深感电子领域之精细与奥秘。

DQS信号的作用与重要性

在DDR4内存模块中,DQS信号充分发挥了其在数据传输中的基准时钟作用。该信号的存在使得数据在不同频率环境下也能够遵循固定的读取或写入次序,从而确保高速传输的准确性与稳定性,特别是面对大规模数据流时。

曾有一回,参与一个项目时,遇到数据传输不稳之困扰。我们深入研究后发现,症结在于DQS信号配置错误。此情此景让人深感,DQS信号对整个系统性能有着深远影响,其作用远非仅限于确保数据准确无误,更是保障系统稳定运行的核心要素。

DQS信号的配置与优化

在内存优化过程中,合理设定DQS信令尤为关键。经过实验验证,适当调节DQS延迟时间、电压及与其他信号间的相位关系,可有效提高内存性能。每一项细微调整均有可能引发性能质变。

在优化某服务器内存性能的项目中,投入了整整一天的时间进行调试,以期设定最优DQS信号参数。虽过程颇具挑战性,然而当发现系统性能得以显著提升的那一刻,我体验到了深深的成就感与满足感。此经历不仅展示了个人的专业素养,同时也充分检验了耐心与细致程度。

DQS信号在实际应用中的挑战

在实践中,DQS信号同样遭受诸多挑战。如,随着内存频率的提升,DQS信号的稳定呈现出更为严峻的挑战。另一方面,各类内存模块及主板之间的兼容性问题亦可能对DQS信号的运行产生负面效应。

在过去的职业经历里,曾遭遇因DQS信号不稳引发的系统崩溃,此问题需具备对硬件深入理解及丰富排障能力方能解决。每遇此类挑战,宛如与繁杂电子领域展开一场智力角逐。

未来趋势:DDR5与DQS信号的进化

随着DDR5内存应用逐渐广泛,其内含的DQS信号正经历全新革新。预计其将更精准、高效率,以满足更高数据传输需求。身为电子工程师的笔者深感期待,坚信此类技术创新将无可疑虑地推动内存技术发展,使DQS信号发挥更大作用。

个人感悟:技术的温度与人性的光辉

深度研究DDR4内存中的DQS信号使我积累了丰富的技术知识,更领悟到技术背后所蕴含的温度与人性。每一项技术变革无不源于无数工程师的辛勤付出及聪明才智。此番经历让我深感身为电子工程师之责任与意义。

总结与展望

通过对DDR4内存中DQS信号的深入研究与实践,我对该领域有了更加全面的认识。其中DQS信号不止是技术层面的细微之处,更为整个内存系统的稳定与高效发挥着决定性作用。期望我的经验体会能为热衷于此领域的同行提供有益参考,并期待未来能看到各类科技突破与创新。

在此,我希望提出一个问题:在您个人的技术探索历程中,哪些技术微妙之处/精细之处给您带来了深刻的影响?敬请于评论区畅所欲言,分享您的经验与观点。让我们共同探讨,携手共进!若您认为此文对您有所裨益,恳请不吝点赞并分享,让更多人从中获益!