身为一位深耕于电脑硬件领域的专家,对内存时序的精准掌握激发了我极大的热忱。DDR4高速内存的时序不仅牵动着电脑运行效率的脉搏,更像驾驭通往数字海洋的航行船舵。今日,在此与同好共享心得体验,希冀能为各位提供有益的借鉴。

初识DDR4高频内存时序

自初涉计算机硬件领域伊始,DDR4内存已逐步推广应用。当时,对内存频率与时序对电脑性能的影响虽有模糊认识,然并未深入理解。直至某次参与计算机硬件研讨活动,一位业界专家详述了DDR4高频内存时序的关键性作用,方使我领悟其中所蕴含的丰富内涵。

为了深入理解时序中各参数如CL(CAS延迟)、tRCD(行地址至列地址延迟)、tRP(预充时间)及tRAS(行激活时间)的意义,我开始广泛查阅相关文献。这些参数的细微变动均有可能对内存性能产生重大影响,使我对该领域产生了浓厚兴趣与敬仰之情。

实践中的挑战与收获

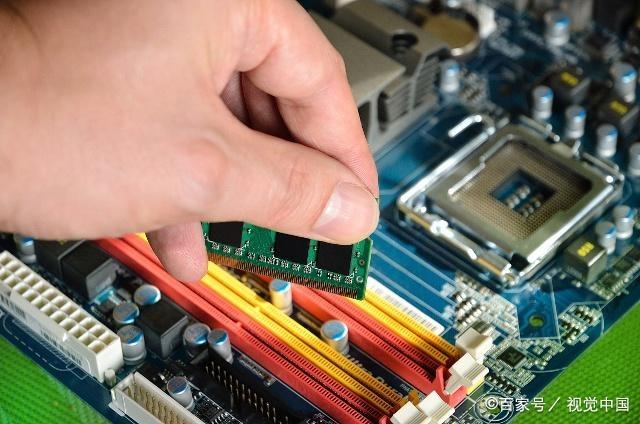

理论与实践相结合,是掌握复杂技术的重要途径。在内存时序调整过程中的首次探索,我记忆犹新。精确设置每项参数,电脑启动更新,观察每次更改的效果,紧张与期待成为主旋律。

在此过程中,我遭遇了诸多挑战。诸如参数设定失准可能引发系统稳定性问题及无法正常开机等现象。面对此情势,难免产生挫败感。然而,当最终寻得最佳时序设置并见证内存性能大幅改善之日,先前所付出的辛劳皆化为甘甜。

高频内存时序的优化策略

深入理解DDR4高频内存时序后,我们归纳了几项优化策略。首先,熟知自家内存颗粒特性至关重要。鉴于每种颗粒对时序的敏感程度大相径庭,须依据实际情况进行微调。

其次,充分运用高端主板的内存时序调控功能。多数此类主板具备多样化的时序设定选择,善用此功能有助于显著提升内存效能。

耐心与细致为调校时序成功之关键要素。每次细微调整均需严谨测试以确保系统稳定及效能最佳化。

从DDR4到未来的展望

随着DDR5内存的广泛应用,内存科技的发展趋势令人瞩目。该产品在频率方面的大幅提高和详细时序调校等方面的革新成果,都预示着未来内存技术必将继续取得突破,为我们更深入的探讨内存规律提供更多可能。

身为一位热爱电脑硬件的学者,我会持续跟踪内存科技的创新前沿,通过深入学习与实际操作,期待为该领域献上一份绵薄之力。

与社区的互动和成长

在此过程中,我深切体会到社区支持之于项目的关键作用。无论面临技术挑战,还是愿意分享个人经验,社区总能适时给予援助并反馈宝贵意见。同时,我热衷于与社区内的同仁保持沟通,共促自身成长。

在深入学术研讨与广泛交流中,我个人的专业素养得以提升,同时也结交了众多有着共同理想的同行者。我们共同研析技术难题,分享宝贵经验,这样的互助过程不仅仅提升了我的学识,更为重要的是,使我深切地体验到学术社区的温馨氛围。

内存时序调整的心得体会

历经磨砺,深入研究与实践使我对内存时序调控有了更深入的领悟。我发现,这不仅仅是技术层面的考究,更是艺术享受的过程。它要求我们具备深厚的硬件知识,精确的参数把控能力以及对细节的极度关注。

在此历程中,我培养出坚韧与毅力品质,更深入理解到成功的愉悦。每次适时调整皆对自我技能的肯定,同时也提升计算机运行效率。

面对未来的挑战

在现代科技的推进下,内存时序调节的复杂度将逐渐升级,面临众多挑战。新式内存技术,繁复的参数设定,以及日益增长的性能需求等问题均需我们审慎处理。

然而,坚信只要我们持续保持对科技的热情与探索,以及持续提升自身的学识素养及实践能力,便能应对各类挑战,引领内存时序调试之路向前迈进。