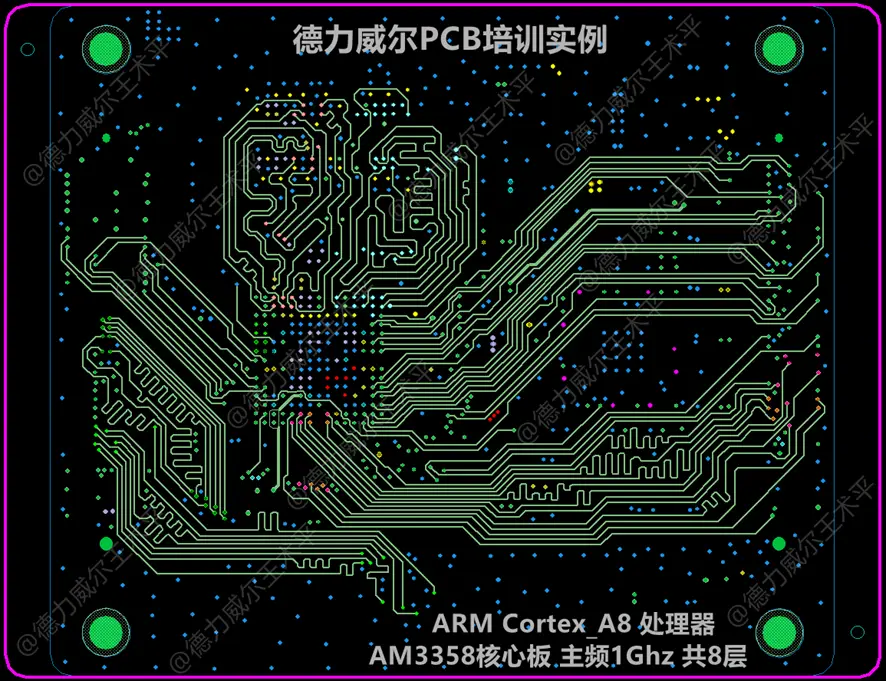

提到DDR走线,心中不免忐忑不安。细看之下,诸多线路杂乱无章地堆砌在一起,令人目不暇接。设计人员必然对此深感困扰,不禁感叹道:“此项工作难度堪称巨大!”随着增加的层数,布线难度随之升级,信号完整性问题愈发复杂,电磁干扰亦层出不穷。这不仅是技术难题,更是对心性的极大考验。

然而,分层数量过多不仅增加了设计难度,同时也提高了生产成本。在每增设一层线路板时,银两便会相应地消耗。无论是PCB板材还是制造工艺,任何的细微变动都将带来实质性的资金投入。除此之外,后期的维修与升级也令人倍感困扰。因此,减少DDR走线层数不仅是技术层面的挑战,也是经济效益的考虑因素。每位设计师都渴望能够减少走线层数,使设计更为简洁明快,降低生产成本,从而提升工作效率。

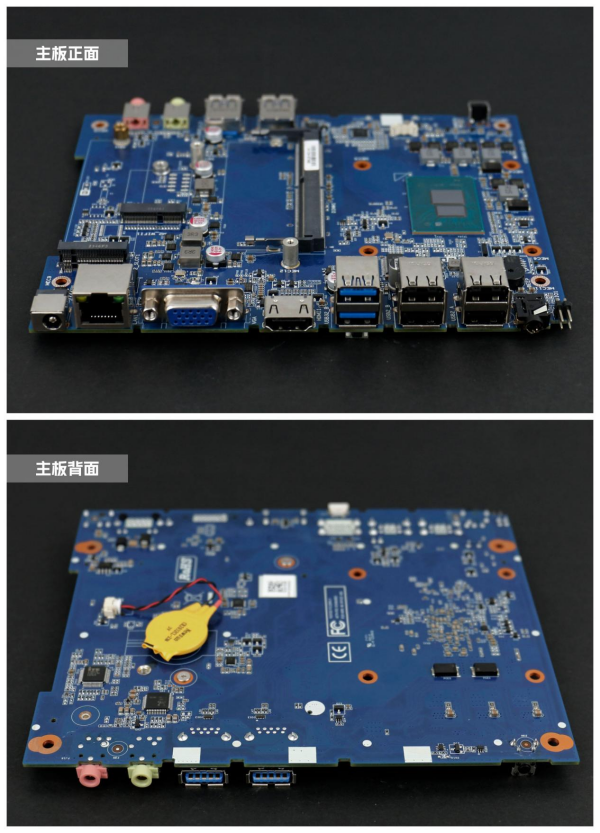

减少层数的第一步:优化布局

为降低DDR布线路径的层次,关键在于对整体布局进行细致规划。精良的布局,将有助于提高设计效率,缩短布线路径长度。举例来说,将DDR芯片及关联部件尽可能紧密地布置在同一位置,便能明显减轻层级负担;同时,充分利用空间结构,防止各器件间过密堆积,从而赋予布线更大的灵活性。有时,仅仅通过微调布局,即可节省大量布线路径层次,这无疑是设计中的一大奇迹。

在设计布线时需注重信号走向,力求直线且无弯绕。如此可缩减线路长度并提升信号质量。有时微小的转角便可能引发额外的走线层。因此,设计阶段务必细心思索,以求线路简洁,进而降低层数成为现实。

利用差分对走线减少层数

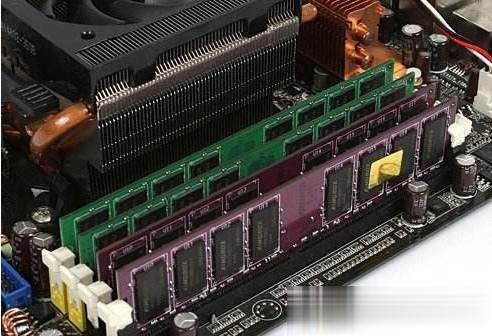

差分对导线,为减少层级提供有效工具。众所周知,差分信号两根导线以对的形式存在,间距与布设颇为考究。精妙地设计差分对布线,可有效降低电磁干扰,提升信号品质,从而在无需增加层级的前提下,达成更优的性能表现。

差分对布线的优势之一在于能够利用其内部的交互作用降低层数。例如,调整差分对间的间距与走向至可使两者在同一层次布线,无需额外增加层级。这既减少了层级数量又简化了设计,达到一石二鸟的效果。因此,运用差分对布线是降低DDR布线层数的有效手段。

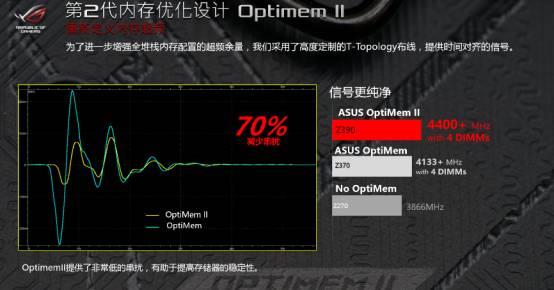

使用拓扑结构优化走线

拓扑设计,看似深奥,实则浅显易懂。即通过精巧安排DDR走线连接方式以降低层级数量。诸如星型拓扑及菊花链拓扑等模式皆可助我们大幅减少布线层次。通过精心挑选适当的拓扑结构,便可使走线更为简练,减少交错与重叠现象,从而在无需额外增加层级的前提下,提升整体性能表现。

运用拓扑结构时需关注信号完整性,因各类拓扑结构对信号产生不同影响,如导致信号延迟或加剧电磁干扰等问题。因此,选择拓扑结构过程中需谨慎分析并进行多次试验,以寻找到最符合设计需求的解决方案,从而实现降低电路层次并保障信号质,的双赢局面。

利用层间走线技术减少层数

层间走线此项先进工艺是在PCB板多层结构中进行科学部署,无需额外增加板层即可实现更众多线路布置。例如,通过调整线路在各层之间穿梭,便可大幅缩减单层通道数量,同样能取得降低板层数目的效果。进一步地说,层间布线能够提升信号隔离度并降低电磁干扰,带来全方位效益。

采用层间走线优化技术时,需注意其层间连接工艺。例如,采用过孔、盲孔或埋孔技术保证各层间的紧密连结。这些连接方式将直接决定走线的品质及性能。因此,实施此技术时,务必精细规划,进行充分实验以寻觅最佳适配自身需求的解决策略。如此可在缩减层级的前提下保持走线品质,实为优秀之选!

减少层数的终极武器:仿真和优化

其精髓在于通过仿真与优化策略,以达到减少层数之目的。运用此类软件,能准确模拟DDR走线性能,挑选出最优走线设计。例如,仿真技术可用于确定最佳走线长度、宽度以及间距等参数,从而在维持层数不变的前提下,显著提升整体性能。

在应用仿真与优化技术之际,务须着重确保仿真数据的精准性及可靠性。由于各种仿真软件所生成的成果存在误差,因此在选用时务必详细评估,开展充分试验以选取最适宜的解决方案。如此便能在降低层级的基础上,保障仿真的精确度,实属可喜。

减少层数的实际案例分析

现身说法,关于实例我有许多精辟见解。譬如,有一次我们设计DDR走线,原本需要四层布线架构,然而通过布局优化、使用差分对走线技术、选择恰当拓朴结构以及运用层间走线等策略,成功将其简化为两层布线,降低了成本且提升了性能,可谓一举两得。

另一次项目中,我们原本需六层的DDR走线设计仅使用四层便达到了目的。实践验证表明,我们有能力降低DDR走线数量,关键在于沉心研究并采取合理措施。

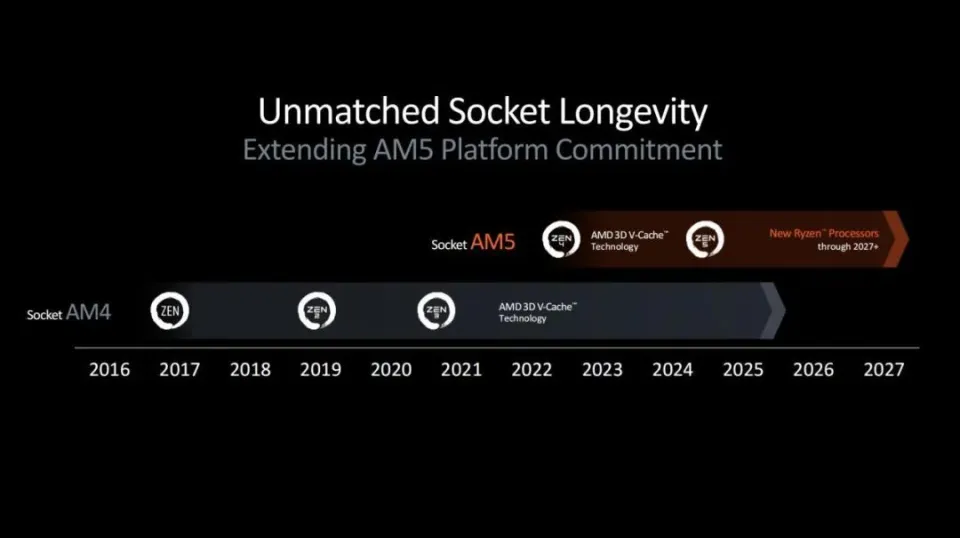

减少层数的未来趋势

展望未来走向,我充满希冀。得益于科技进步,诸多降低DDR走线层数的策略将日益丰富且成效显著。例如,崭新的材料与工艺、创新性的设计方案均有助于大幅度削减层数,显著提升性能指标。同时,借助人工智能及机器学习等尖端技术,仿真与优化的精准度亦将不断攀升,令人振奋不已!

因此,降低DDR布线层次并非仅关乎技术层面,实质上是创新过程中的重要环节。只要坚持创新与实践,必将找出更多降低层级的途径,从而达成更为出色的性能表现。如此一来,我们便可使设计变得更加便捷,共同创造一个更美好的世界,实在令人欣喜不已!

深入探讨降低DDR走线层数的策略无疑引人关注。通过精心布局、采用差分对布线方式、精选拓扑结构,结合层间走线手段以及进行精细的仿真与优化,无需增大层数便可获得卓越性能。实践案例分析证实,减少层数并非遥不可及,只要我们全力以赴,必定能够取得成功。因此,让我们携手共进,致力于降低DDR走线层数,使设计过程更为便捷,共同创造更加美好的未来!

在此,请教各位一个问题:在降低DDR布线层数期间,有哪些困境阻碍了您的进程?又采用何种策略进行了解决?期待在评论区共享您们的宝贵经验,共同探讨与提升。同样,若本篇文章能提供您所需的信息,恳请您慷慨地给予点赞及分享,让更多人受益,共同为全球和平尽一份力!