高速DDR3与DDR4内存接口的布线策略在现代电子系统设计中扮演着至关重要的角色,直接关系到系统的性能与可靠性。本文旨在全方位解析高效DDR3/DDR4电路布线方法,旨在提升工程师对该技术的深入理解和实际应用能力。

1.理解高速DDR3/DDR4的基本特性

在当代计算机体系结构中,高速DDR3与DDR4内存接口发挥着举足轻重的作用。DDR3与DDR4分别指代了第三代与第四代双倍数据率同步动态随机存取存储技术,两者的核心差异体现在数据传输速度和能耗上。DDR4相较于DDR3,在数据传输速度上有所提升,同时能耗更低,然而这也对布线设计提出了更高的要求。

在布线设计领域,掌握DDR3与DDR4的核心属性至关重要。DDR3的运行频率普遍介于800MHz至1600MHz,而DDR4的频率上限可至2133MHz至3200MHz乃至更高。此高频特性使得布线设计需全面考量信号完整性、时序同步与电源稳定性等多重因素。

2.信号完整性:确保数据传输的可靠性

在高速DDR3/DDR4线路布局中,信号完整性问题占据关键地位。鉴于数据传输频率之高,信号在传播途中极易遭受干扰、反射以及串扰的侵袭,进而引发数据失误。为确保信号无损害,线路设计必须恪守一系列基本准则。

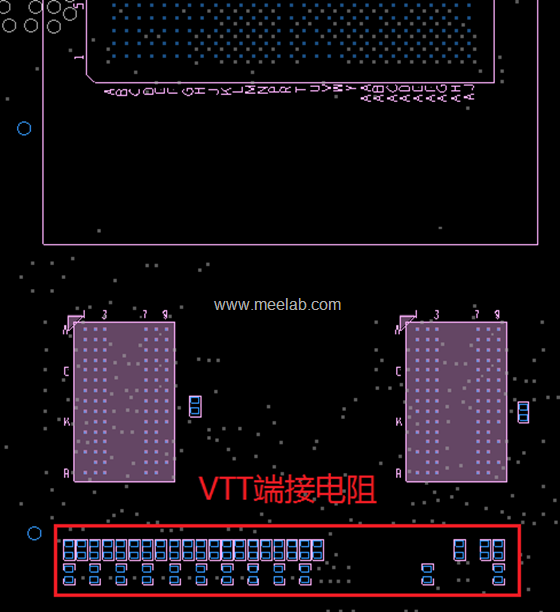

确保布线长度均等以降低信号时序误差,同时,采纳差分信号传输技术以增强对噪声及串扰的抵御能力。另外,实现阻抗匹配对于保障信号完整性至关重要,通常采用50欧姆标准阻抗进行布线设计。

3.时序匹配:精确控制数据传输时间

时序同步对于高效DDR3/DDR4线路布局而言至关重要。鉴于DDR3与DDR4运行频率极高,数据传输的时机极为紧凑,哪怕是极小的时序误差也可能引发传输故障。故此,在布线布局阶段,对数据传输时机的精确掌控不可或缺。

为确保时序同步,布线布局中必须重视信号传播的时延。一般而言,应尽量使布线长度均衡,以达成各信号传播时延的均等。同时,借助时钟信号同步技术与时钟树优化,也是达成时序匹配的关键策略。

4.电源完整性:稳定供电是基础

电源完整性构成高速DDR3/DDR4布线设计的关键要素。鉴于DDR3及DDR4的运行频率极为之高,对电源的稳定性及噪声控制标准亦极为严苛。任何形式的电源噪声均可能引发数据传输失误,故在布线设计阶段,必须严格保障电源的完整性。

为确保电源系统的完整性,布线方案应采纳多层板结构,并在电源与地平面之间增设去耦电容器。同时,设计合理的电源分配网络对于维护电源完整性至关重要,一般推荐采用星型或菊花链式的电源分配拓扑。

5.布线策略:优化布线路径

高速DDR3/DDR4布线设计中的核心要素是布线策略,恰当的布线策略能显著降低信号反射与串扰,进而增强系统性能与稳定性。在进行布线设计时,务必恪守一系列基本准则。

为确保信号传输效率,布线应追求最短路径,降低传输时延。同时,线路应保持直线,以降低信号反射与串扰。再者,应尽量避免穿越噪声密集区,以维护信号完整。

6.仿真验证:确保设计的正确性

仿真测试构成高速DDR3/DDR4布线设计的终末阶段,且为验证设计准确性的核心步骤。此过程能够复现实际作业环境下的信号传输状况,进而识别并消除潜在的缺陷。

仿真验证过程中,通常依赖诸如HyperLynx或SIwave等高级仿真软件。借助这些软件,可实现信号完整性、时序同步及电源完整性等多维度仿真分析,进而保障设计结果的准确性。

7.实际应用中的注意事项

在实施DDR3/DDR4高速布线方案时,必须充分关注特定情境。譬如,鉴于不同供应商的DDR3与DDR4芯片存在差异化的电性属性和时序规范,布线设计阶段务必参照对应的技术手册。

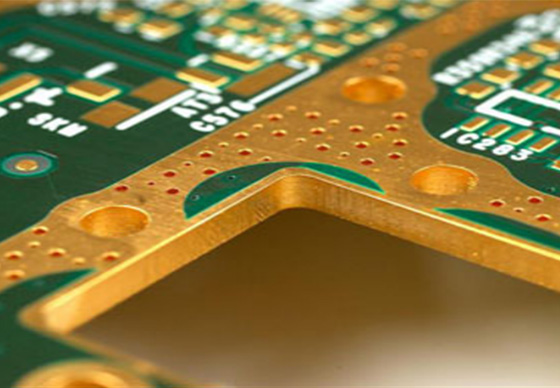

在实施过程中,必须考虑PCB生产技术的约束因素。具体而言,对于布线宽度与间距的选定,必须遵循PCB生产的最小线宽与最小间距标准,从而保障设计方案的制造可行性。

在进行高速DDR3/DDR4线路布局过程中,您遭遇了哪些难题?敬请于评论区交流您的实战心得与独到观点,以便共同研究更高效的挑战应对策略。