在FPGA(现场可编程门阵列)与DDR(双倍数据率同步动态随机存储器)协同应用过程中,存在一系列挑战。以下内容将对此进行细致剖析,分为六个关键方面进行阐述。

DDR初始化问题

在FPGA上对DDR进行初始化操作至关重要。首先,初始化过程中的时序必须精确对应,若时序出现混乱,DDR将无法实现正常运作。在诸多项目中,因时钟信号存在偏差以及复位信号的不稳定性,DDR的初始化过程往往失败,进而导致整个系统陷入停滞状态。其次,初始化参数的设定同样复杂,不同型号的DDR在数据传输速率、位宽等关键参数的配置上要求极高,任何微小的误差都可能引发后续的读写错误。

DDR的启动过程并非易事,它要求对FPGA及DDR芯片的内在特性有深刻理解。在硬件设计阶段,寄存器的设置必须精确无误,任何微小的误差都可能导致故障。以某一产品的大规模生产为例,就曾因电源波动导致初始化时分频器未能提供准确的时钟频率,致使DDR启动失败,这一案例充分说明,每一个细节均不容忽视。

读写一致性问题

FPGA与DDR之间的读写交互过程极为繁复。一方面,鉴于FPGA的高并行特性,多个读写请求可能同时涌现,这就要求我们精心构建读写请求的仲裁机制。在部分复杂的逻辑设计中,当读写信号同时抵达DDR控制器之际,若无恰当的仲裁策略,极易引发数据冲突。另一方面,读写数据的顺序亦需确保准确无误。若顺序出错,将导致数据混乱,进而影响上层应用结果的准确性。

在具体应用场景中,例如图像数据存储过程中,若读写顺序出现错误,则可能导致图像出现杂乱纹理等问题。此外,FPGA内部各个模块对于DDR的读写权限可能需要设置不同的优先级,若处理不当,部分关键数据的读写操作将无法及时完成,进而影响系统整体性能表现。

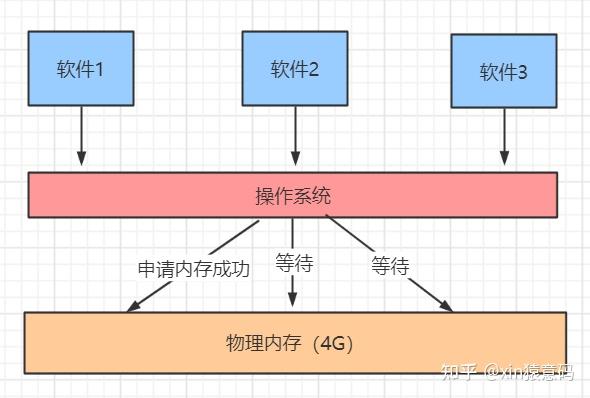

带宽利用率问题

DDR的带宽属于一种有限的资源,其理论带宽主要受到数据线宽度和频率的影响。然而,在实际应用中,FPGA的工作模式往往未能充分利用这一带宽潜力。以FPGA在数据传输过程中的突发长度设置为例,若设置过短,将导致DDR带宽无法得到充分填充。此外,数据传输过程中的等待时间等额外开销亦显著影响了带宽的实际有效利用率。

在涉及多媒体处理的应用场景中,若视频数据量庞大且需频繁进出DDR,若带宽使用效率较低,则可能导致视频播放出现卡顿。为此,设计者需对FPGA的存储访问模式进行优化,例如采用批量数据传输、数据预取等策略,以提升带宽使用效率。若未对此问题予以足够重视,在数据传输速率要求较高的应用场合,DDR将无法达到所需性能标准。

时序约束问题

DDR与FPGA的协同作业对时序的准确性极为关键。其中,数据传输的时序安排尤为关键。在FPGA对DDR进行读写操作时,若数据建立与保持时间未达到DDR的规范要求,将导致数据无法准确写入或读取。在高速系统运行过程中,这一问题尤为突出。此外,时钟信号的时序亦不容忽视。时钟偏差、时钟树布线延迟等因素均可能引发时序问题。

在电路板设计过程中,若布线设计不合理,例如存在过长的连线,将可能引发时钟信号延迟及信号失真等时序性问题,进而干扰DDR的稳定运行。为此,工程师必须实施精确的布线策略,并开展时序性分析,以保证时序参数符合既定标准。若时序参数超出规定范围,即便硬件其他部分运作正常,DDR模块亦难以实现稳定工作。

掉电数据保护问题

在DDR数据管理中,掉电保护机制至关重要。硬件设计上,必须构建稳定的掉电监测电路,并在掉电事件发生时迅速激活备用电源或触发警报系统。若掉电监测反应迟缓,将可能造成DDR内部正在处理或尚未存储的数据丢失。此外,软件层面亦需采取相应措施,如在特定应用场合确保数据回写操作的有序执行。

在航天领域的数据采集设备设计中,若配备有FPGA与DDR芯片,一旦卫星在发射或升空过程中遭遇电源波动或断电等紧急情况,若无健全的断电保护措施,众多至关重要的数据信息将不可避免地永久消失,从而对航天任务中数据依赖的关键环节造成严重缺陷。

兼容性问题

FPGA与DDR的兼容性涉及硬件与软件双重层面。就硬件而言,FPGA的引脚配置需与DDR接口相契合。若FPGA的IO电平规范与DDR的输入输出电平存在不匹配,则可能导致数据误判。在软件层面,FPGA的逻辑设计需与DDR的读写协议相兼容。若对协议理解存在偏差或实现出现误差,将引发FPGA与DDR间通信故障。

在产品升级换代过程中,替换了新型DDR芯片,然而,由于未充分评估FPGA与该新芯片在软件协议层面的兼容性,致使系统完全无法启动。此事件警示我们,在全新设计或升级项目中,兼容性因素必须得到细致的考量。

本段内容涵盖了FPGADDR相关问题的核心要点,旨在为您提供有益的信息。在您执行FPGA项目过程中,是否遭遇过DDR领域的难题?如本文对您有所裨益,敬请给予点赞与转发。