本文将深入剖析Vivado软件平台中DDR调试技术的具体应用及操作流程。

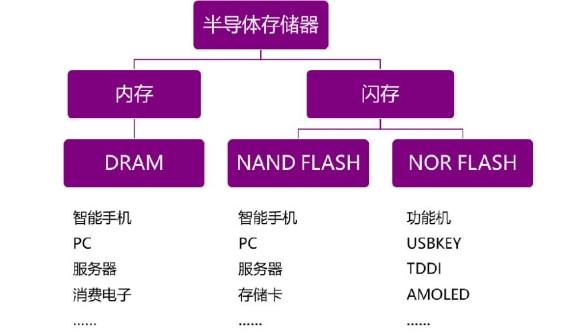

DDR简介与重要性

DDR(双倍数据率)内存对当代电子系统的发展至关重要,其高速读写能力显著增强了系统整体性能。一方面,DDR的高效传输特性使得数据能在各模块间迅速流通,极大地提升了计算机、FPGA开发板等设备的运行效能。另一方面,在众多复杂应用领域,如图像视频处理、高速数据采集等,DDR的性能在很大程度上决定了项目的成败。

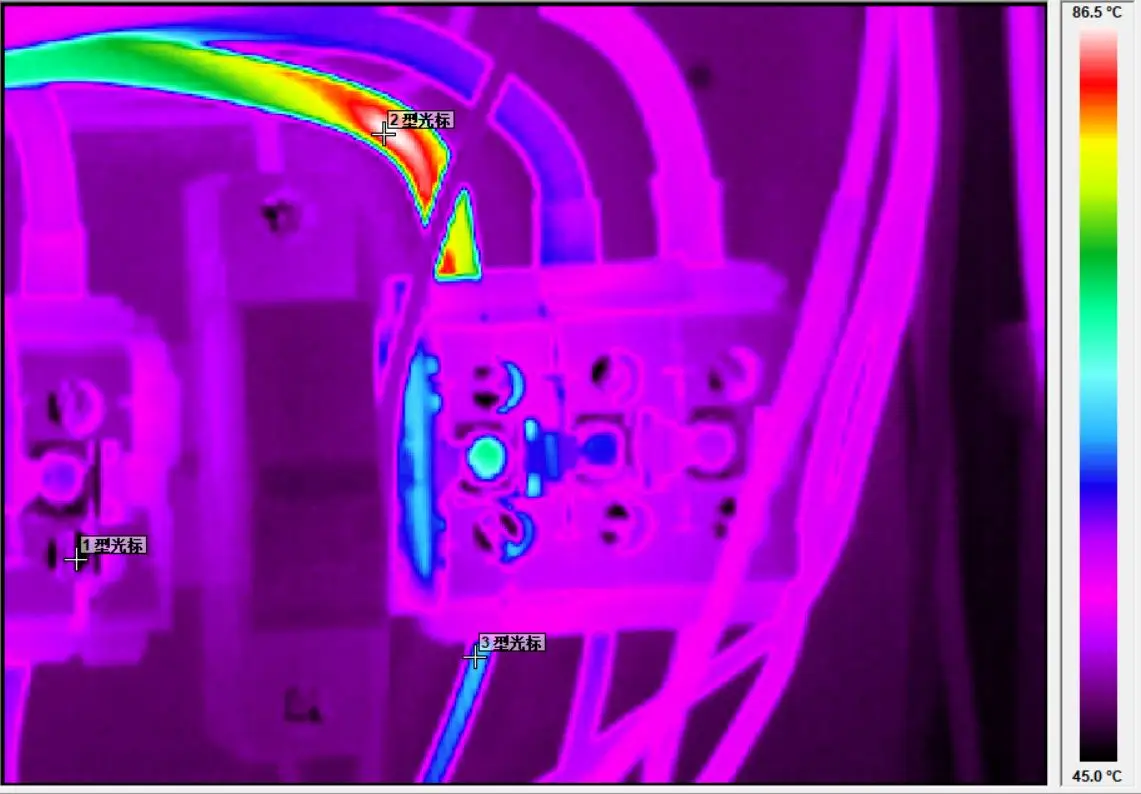

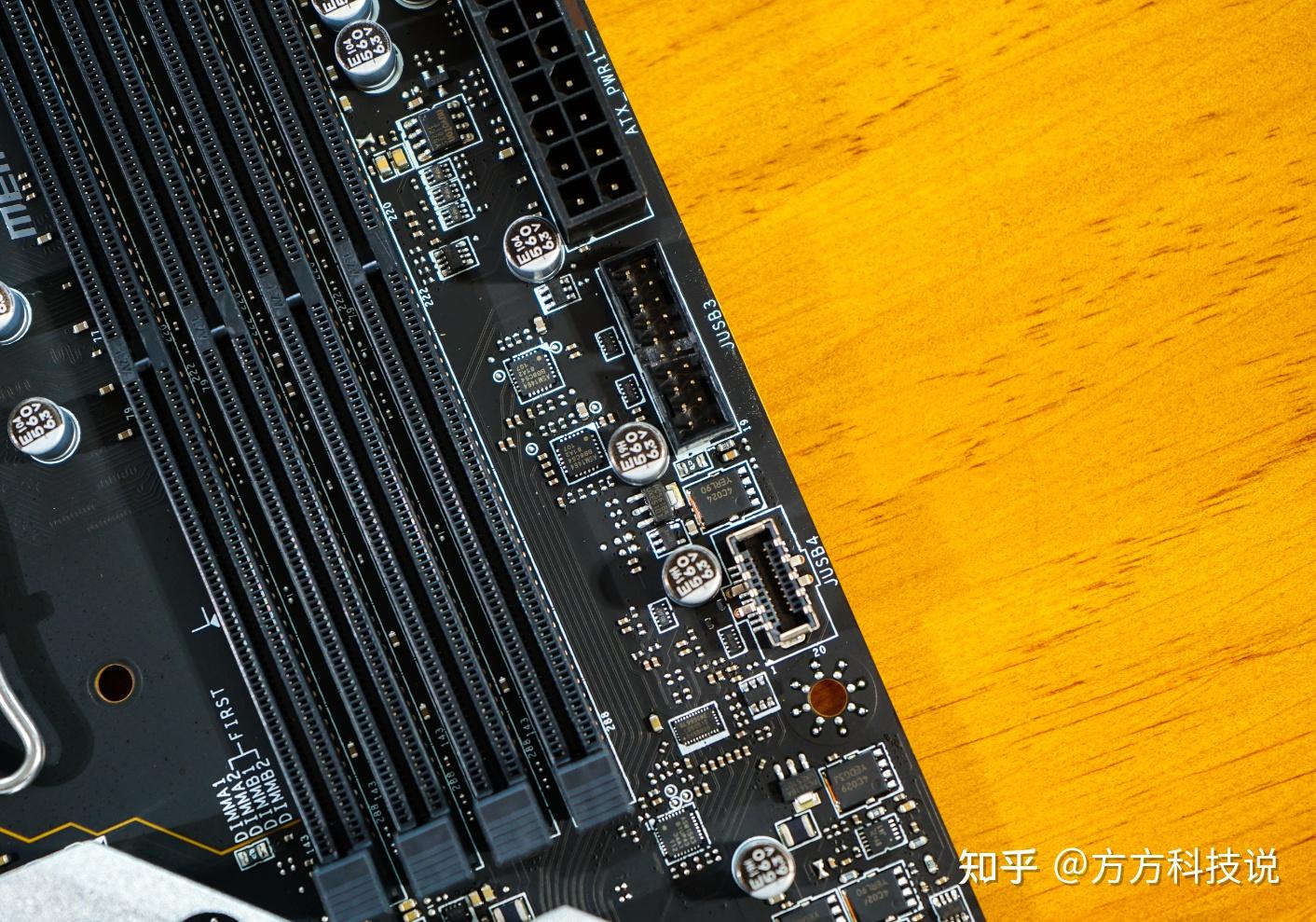

在硬件电路设计中,DDR的连接方式至关重要。若其与其他组件的连接线路设计不当,将可能引起信号完整性的损害。此类问题可能导致数据错误、读写操作失败等不良后果。通常情况下,必须对布线进行周密规划,遵循特定的电气规范,以确保DDR能够稳定运行。

Vivado环境下DDR的设置

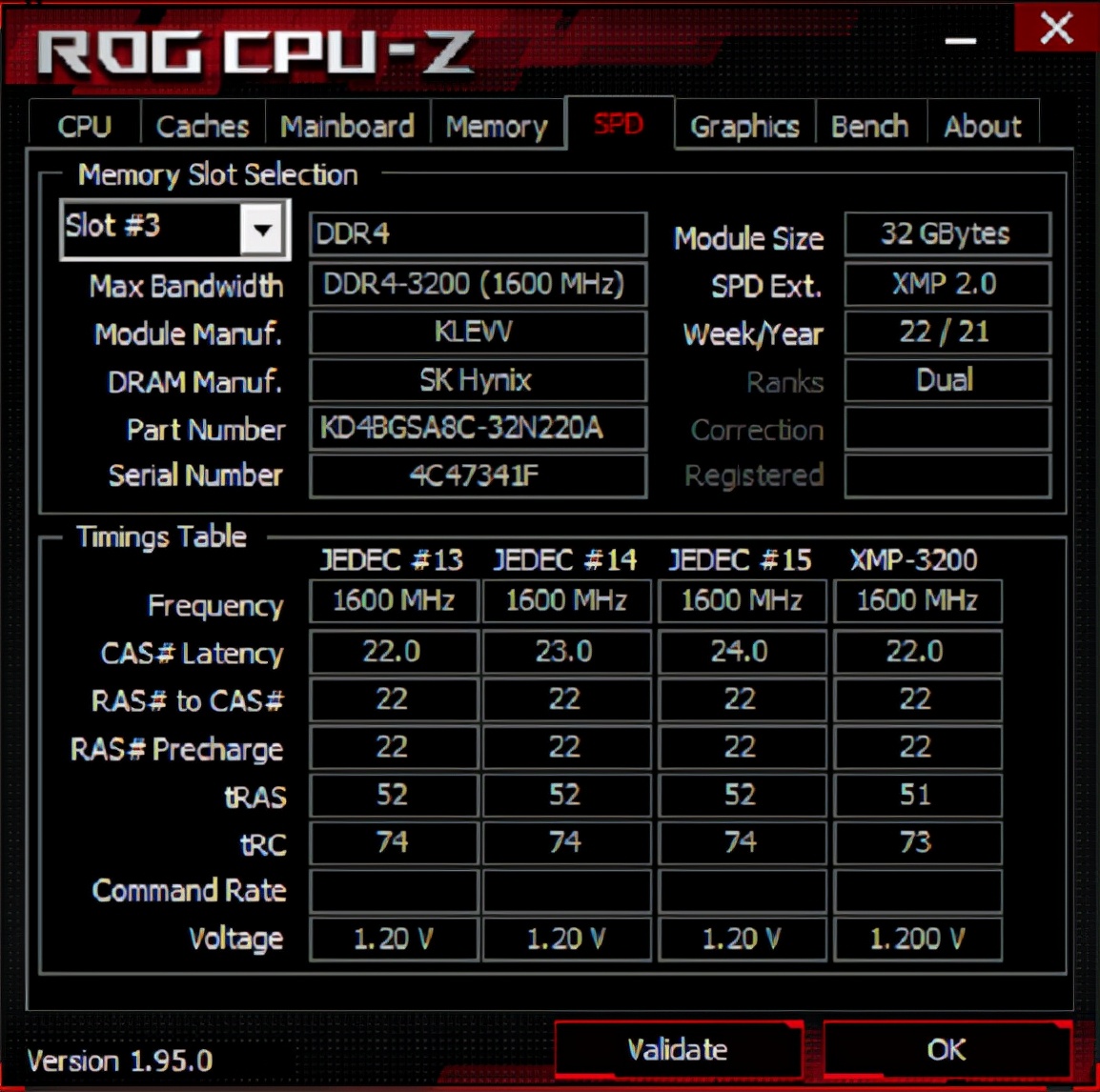

在Vivado软件中,构建新项目或激活现有项目构成了DDR配置流程的首要环节。在项目初始化阶段,针对DDR相关组件,如控制器等,务必进行精确的型号选择。此选型需基于目标硬件平台的具体要求以及DDR芯片的具体型号。

随后,重点在于对DDR控制器的各项参数进行细致设置。这一环节涵盖了数据位宽、地址映射等众多关键参数。其中,数据位宽的设定直接决定了每次数据读写过程中传输的数据量,而地址映射则关乎数据在DDR存储空间中的具体存储位置,这两者均对DDR在系统中的运行效能产生直接影响。在调整这些参数时,任何微小的失误都可能导致DDR无法正常运行。

DDR初始化过程

DDR的启动过程至关重要,必须遵循严谨的步骤执行一系列预备动作。首要步骤为复位,此过程相当于赋予DDR一次全新的起点,旨在消除先前可能遗留的杂乱无序状态。复位操作完毕后,紧接着必须进行一系列的校准步骤。

校准作业涉及诸多繁复环节,其重要性不容忽视。其中,对ODT(片上终结)的精确校准尤为关键,它直接关系到数据传输线路的信号品质。此外,时钟校准亦至关重要,时钟在DDR运行中扮演着节拍器的角色,精确的时钟校准确保数据传输能在恰当的时序中进行。若初始化阶段发生错误,将对DDR数据读写造成严重影响。

DDR的读写操作调试

在进行DDR的读写操作过程中,首要任务是准确掌握读写流程的规范。读取数据时,必须借助特定地址从DDR中提取信息,而写入数据则涉及将数据存入DDR的指定地址空间。尽管这一过程表面上看似简单,但在实际操作中,却可能受到众多因素的干扰和影响。

在读写过程中若发生失误,务必从多角度进行详尽检查。首先,针对硬件层面,需核实连接线路是否遭遇信号传递障碍。其次,在软件层面,应审查读写地址的算法逻辑是否准确无误,以及数据使能信号是否处于正常状态。偶尔,即便是读写地址数值的一点点偏差,也可能导致读写数据出现异常现象。

常见DDR调试问题及解决

在DDR调试过程中,频繁遭遇诸多典型故障,其中之一便是数据传输失误。遭遇此类问题时,首要任务是核实硬件电路中的信号完整性,这涵盖了检查是否存在串扰以及布线是否遵循电气规范等方面。

常见困扰之一涉及DDR的读写速度与预期值有所出入。此时,可能需对时钟频率以及DDR控制器的时序参数进行相应调整。有时,时钟频率超出了DDR的承受极限,进而引发数据错误;亦或是时序参数设置不当,导致DDR未能充分发挥其最高速度性能。

DDR调试工具在Vivado中的使用

Vivado平台配备了一系列高效的调试辅助工具,旨在协助用户进行DDR内存的调试工作。其中,波形查看器是一项关键功能,用户能够借助该工具直观地观察DDR系统中各类信号的波形变化,包括时钟信号、读写控制信号以及数据信号等。

具备逻辑分析集成模块。此模块可对DDR运行过程中的诸多逻辑状态进行深入解析。通过运用此类工具,我们得以迅速锁定DDR调试中的问题所在,极大提升调试效率,摆脱了以往在未知领域摸索的困境。

本文旨在为读者在Vivado平台进行DDR调试提供有益参考。在DDR调试过程中,你是否遭遇过一些极具挑战性的难题?期待各位朋友积极点赞、转发,并在评论区畅所欲言,共同探讨。