FPGA,即现场可编程门阵列,从DDR2升级到DDR3的转换过程颇具挑战性,却也充满意义。这一过程涉及众多领域的知识,诸如FPGA的内部构造、DDR2与DDR3的特性,以及信号处理等多个方面。接下来,我将从多个角度对这一转换过程进行详细解析。

了解DDR2和DDR3特性

DDR2和DDR3存在显著的不同。DDR2在速度、功耗和容量方面与DDR3有所差异。DDR2的频率偏低,能效表现不佳。比如,在老旧的FPGA项目中使用DDR2可能会限制数据处理的速度。相比之下,DDR3拥有更高的频率、更低的功耗和更大的容量。在图形处理等对数据处理有较大需求的应用中,DDR3的表现更为出色。在进行这种转换时,我们必须充分了解这些特性的差异。为此,我们需要深入研究两者的芯片手册等相关资料,以便制定出正确的转换方案。

在转换过程中,必须充分考虑到成本这一关键因素。尽管DDR3内存的性能更为出色,但若项目对成本控制要求极高,那么就需仔细衡量,看是否真的需要进行转换。

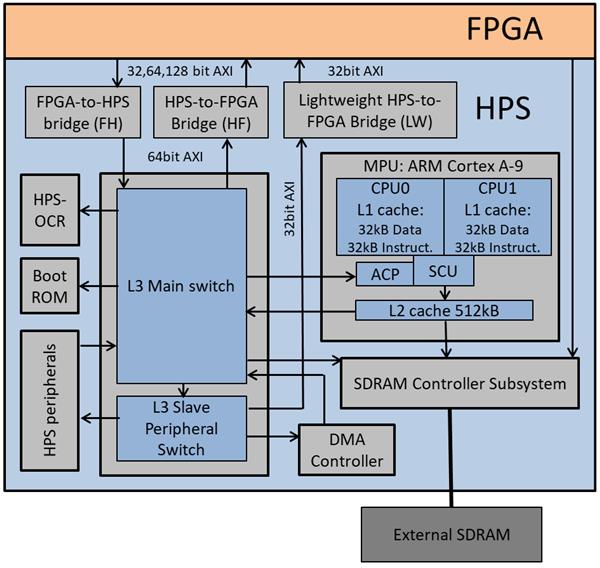

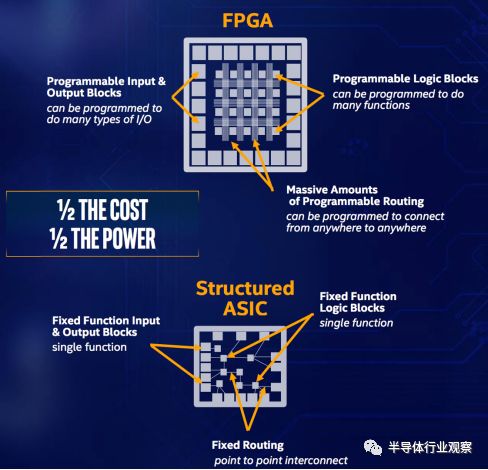

FPGA内部结构调整

DDR3与DDR2的特性存在差异,因此FPGA内部结构必须作出调整。首先,逻辑布局必须重新规划。DDR3的高速信号传输需要更为严格的布局布线规则。若继续使用DDR2的逻辑布局,可能会导致信号干扰等问题。比如,若数据线和时钟线的距离安排不当,将影响信号传输的准确性。此外,部分控制逻辑也需要调整。DDR3的读写模式与DDR2不同,因此FPGA内部关于内存读写控制的逻辑单元需要重新设计。这要求对FPGA的可编程逻辑资源有深入的理解。

面对资源紧张到极点的FPGA,这样的调整无疑是一项艰巨的挑战。我们必须仔细权衡资源的分配,以免资源短缺引发功能缺失的问题。

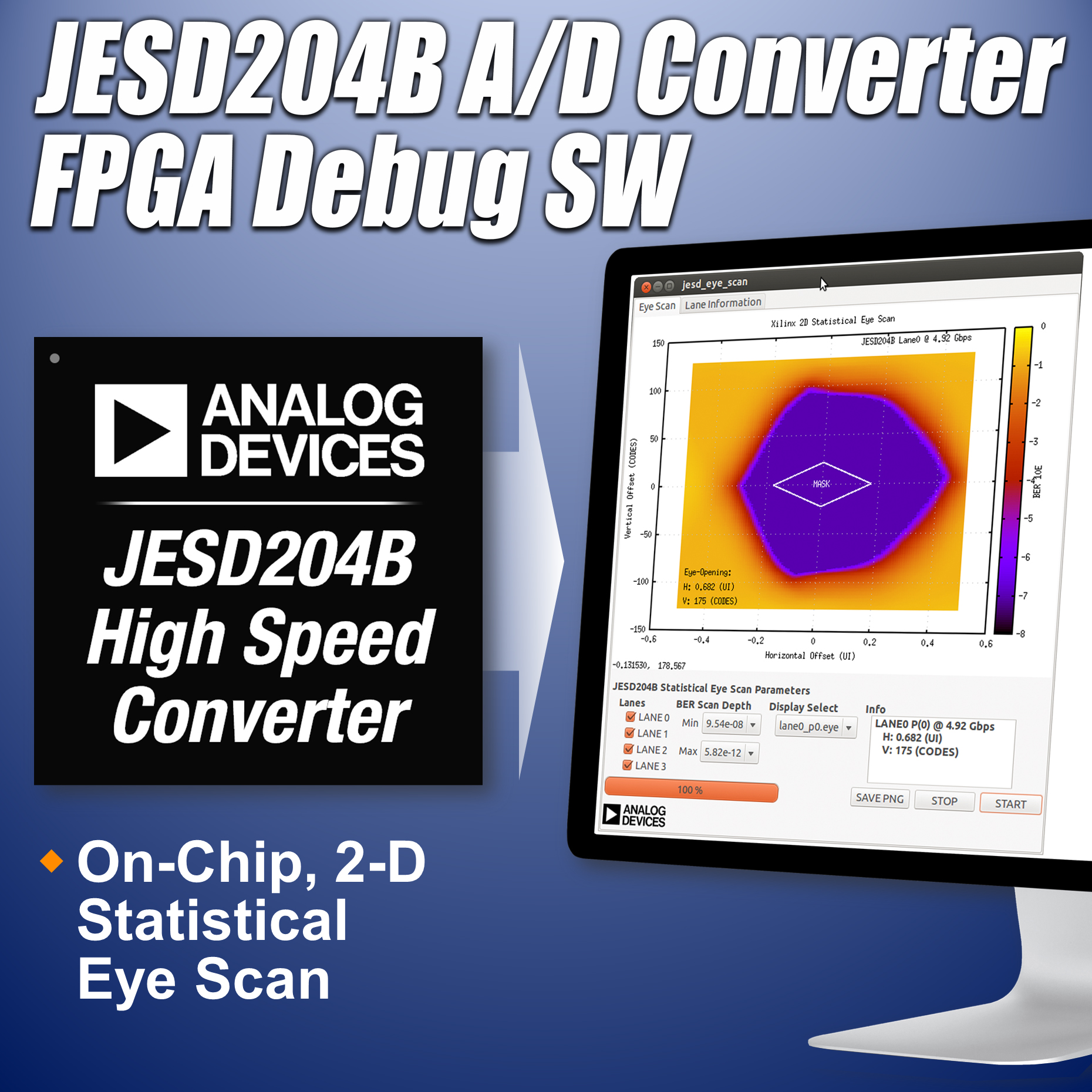

信号处理的变更

在DDR2升级至DDR3的过程中,信号处理至关重要。DDR3对信号的电压幅度、上升沿和下降沿时间等都有明确的要求。首先,端接电阻的配置必须重新审视。DDR3可能需要不同阻值的端接电阻以适应其信号传输特性,若沿用DDR2的端接电阻配置,将导致信号反射加剧,从而影响信号完整性。此外,信号的时序约束也更为严格。DDR3的高速特性要求信号间的时序关系更加精确,包括数据的读写时序,以及时钟信号与数据信号之间的偏移关系,这些都不可有丝毫误差,这对信号处理提出了更高的挑战。

在实际的工程实践中,工程师们必须解决一个难题,那就是如何精确测量并调整信号,以确保其符合DDR3的标准要求。

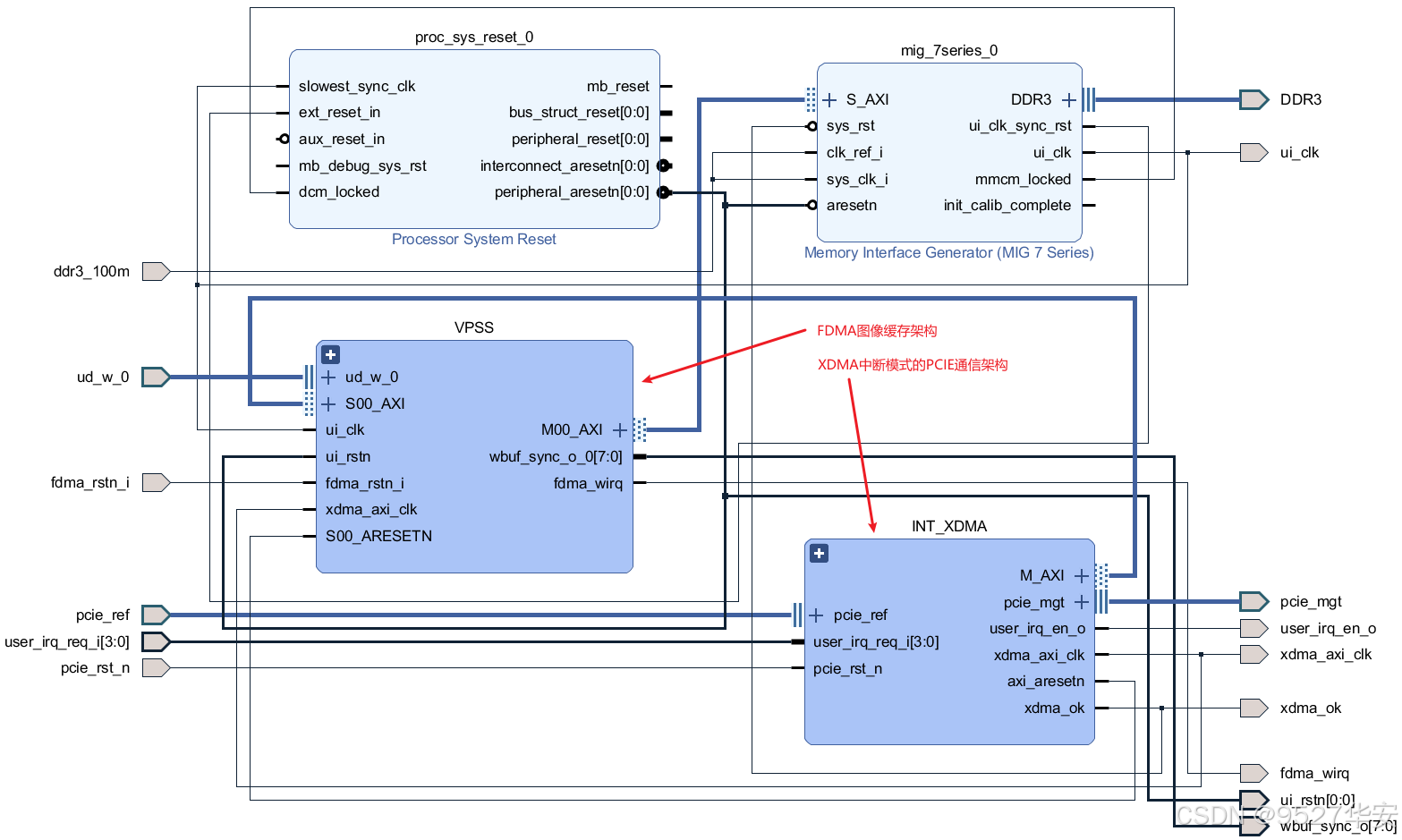

软件代码的修改

相关软件的代码必须进行修改。首先,FPGA的配置代码要调整,因为DDR3的初始化配置与DDR2大相径庭。必须依照DDR3的初始化序列编写代码,这包括正确设置各种寄存器参数,这样才能确保DDR3能够正常运行。其次,顶层逻辑的代码也需要调整。DDR3的读写逻辑发生变化,这影响了数据读写、存储管理等功能的代码,因此这些代码必须重新审查并重新编写。比如,可能需要对存储器中的数据地址映射进行修改,以适应DDR3的存储架构。

工程师必须进行大量测试,以确保代码修改后的准确性。同时,我们还需思考如何高效开展这项测试工作。

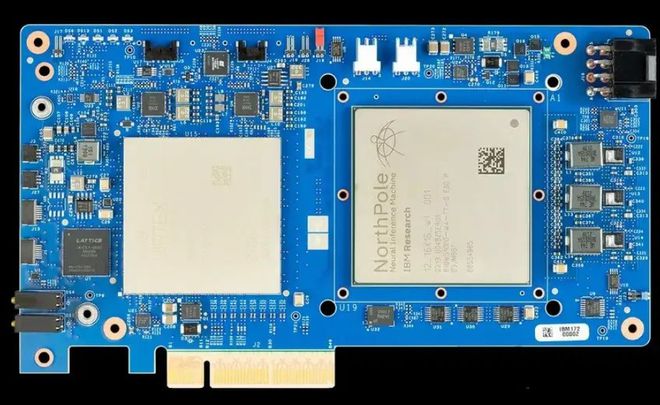

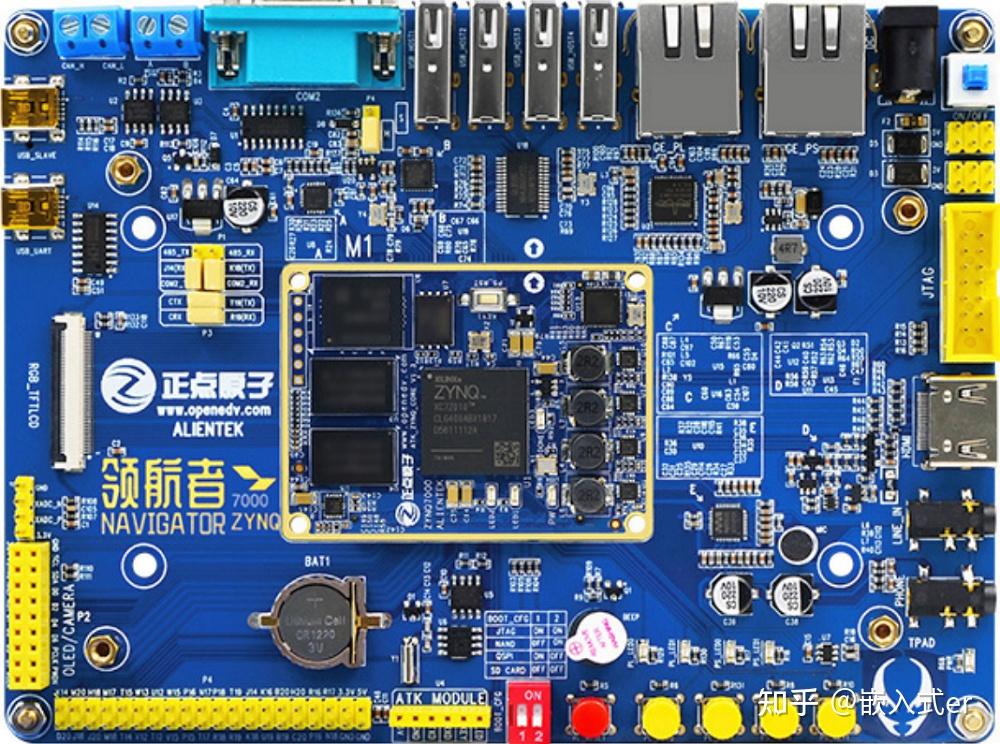

硬件电路的适配

硬件电路必须兼容DDR3标准。其中,电源电路是至关重要的组成部分。DDR3的功耗特性对电源供应的稳定性与效率提出了更高要求,可能需要通过升级电源芯片或增加滤波电容等措施来满足这些需求。同时,板级布线规则也发生了变化。DDR3的高速信号传输需要严格遵守更严格的布线长度控制、差分线对匹配等规范。例如,若布线长度不匹配,可能会导致信号差分偏移,进而影响传输效率。

硬件工程师与PCB设计工程师需紧密协作,这样才能共同探寻出最适宜DDR3的硬件电路设计方案。

兼容性和可扩展性

在转换DDR2至DDR3的过程中,必须兼顾兼容性和扩展性。特别是一些大型系统,可能还含有依赖DDR2的模块,此时,如何确保DDR3模块与之相容,便成为一个难题。比如,可能需要增设转换接口模块,以保证数据交换的准确性。此外,还需预见到未来的扩展需求。尽管当前项目仅要求完成DDR2到DDR3的转换,但未来可能会有更高的内存需求,因此,设计方案必须具备良好的扩展潜力。

这里有一个问题想请教大家,那就是在实际进行FPGADDR2至DDR3转换过程中,大家遇到的最难解决的问题究竟是什么?欢迎在评论区分享您的经验,同时,也请您为这篇文章点赞并转发。