简单来说,DDRCPU的原理,关乎计算机内存与中央处理器间数据交互的关键规则和实现技术。这构成了计算机高效运行的基础。对此有深入理解,将有助于我们更深入地探究计算机底层的运作逻辑。

DDR与CPU通信基础

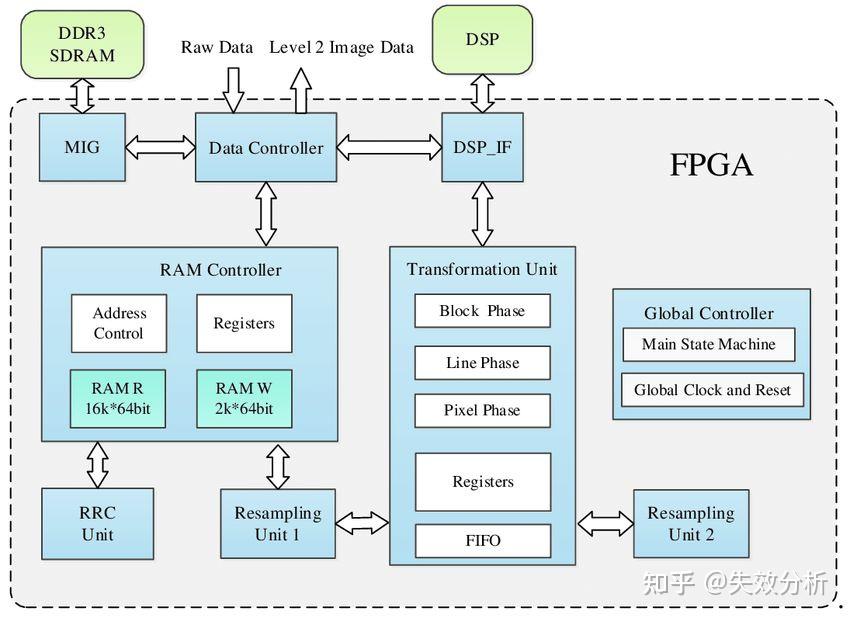

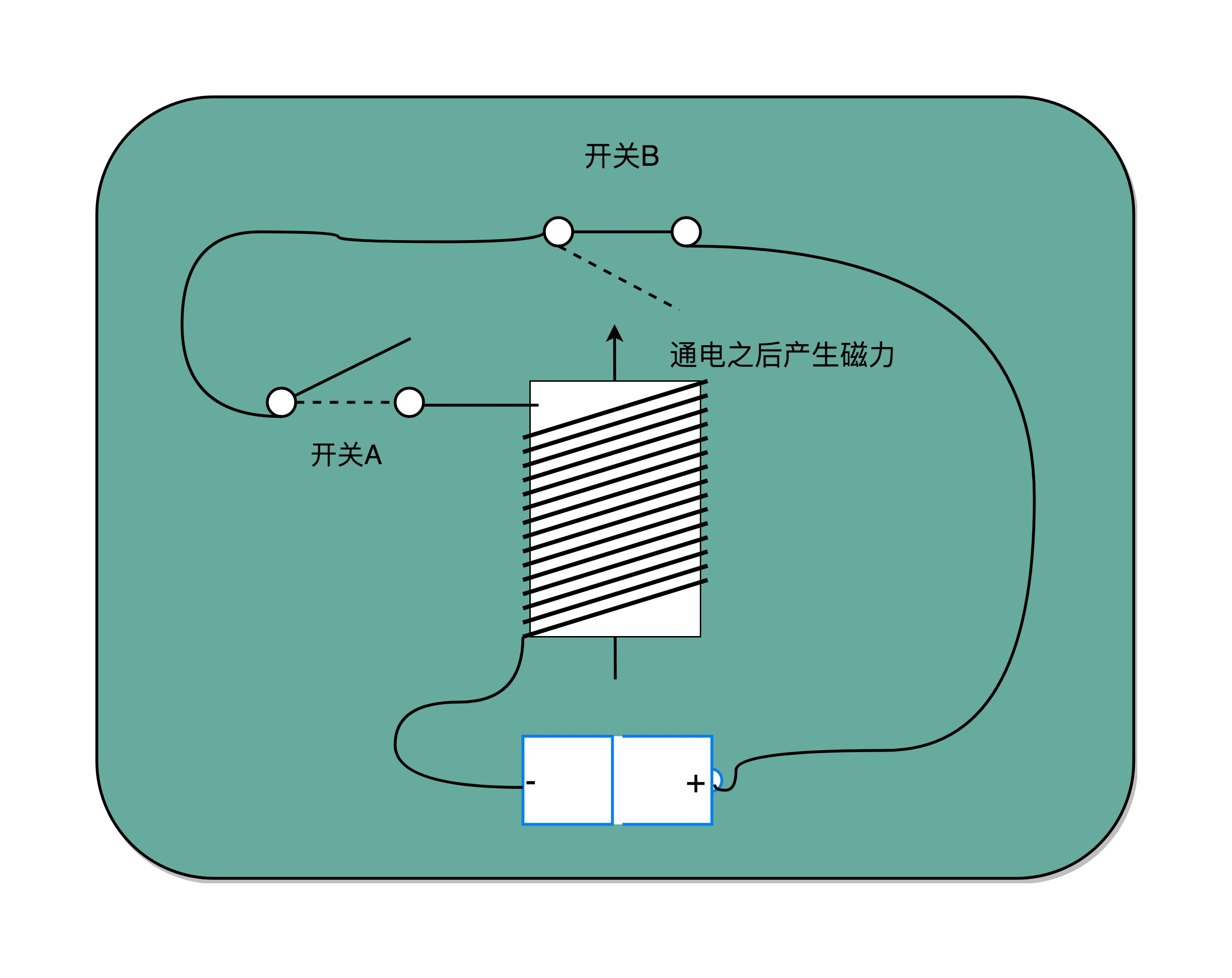

DDR,这是一种内存技术,主要功能是临时存储数据。它与CPU的沟通主要通过特定的线路和信号传输协议来完成。DDR具备预取功能,每个时钟周期都能提前获取数据,这使得它能够迅速应对CPU的数据需求。而且,当CPU发出读取或写入指令后,DDR必须在规定的时间内完成操作,这样才能确保电脑运行顺畅。如果在实际使用中DDR与CPU的通信出现延迟,就会导致程序运行不畅,出现卡顿的情况。

DDR设计用于与CPU高效交换数据,因此选择了双数据速率技术。这样一来,数据传输不仅能在时钟信号的上升沿进行,还能在下降沿进行,与单数据速率相比,这一设计显著提升了数据传输的效率。

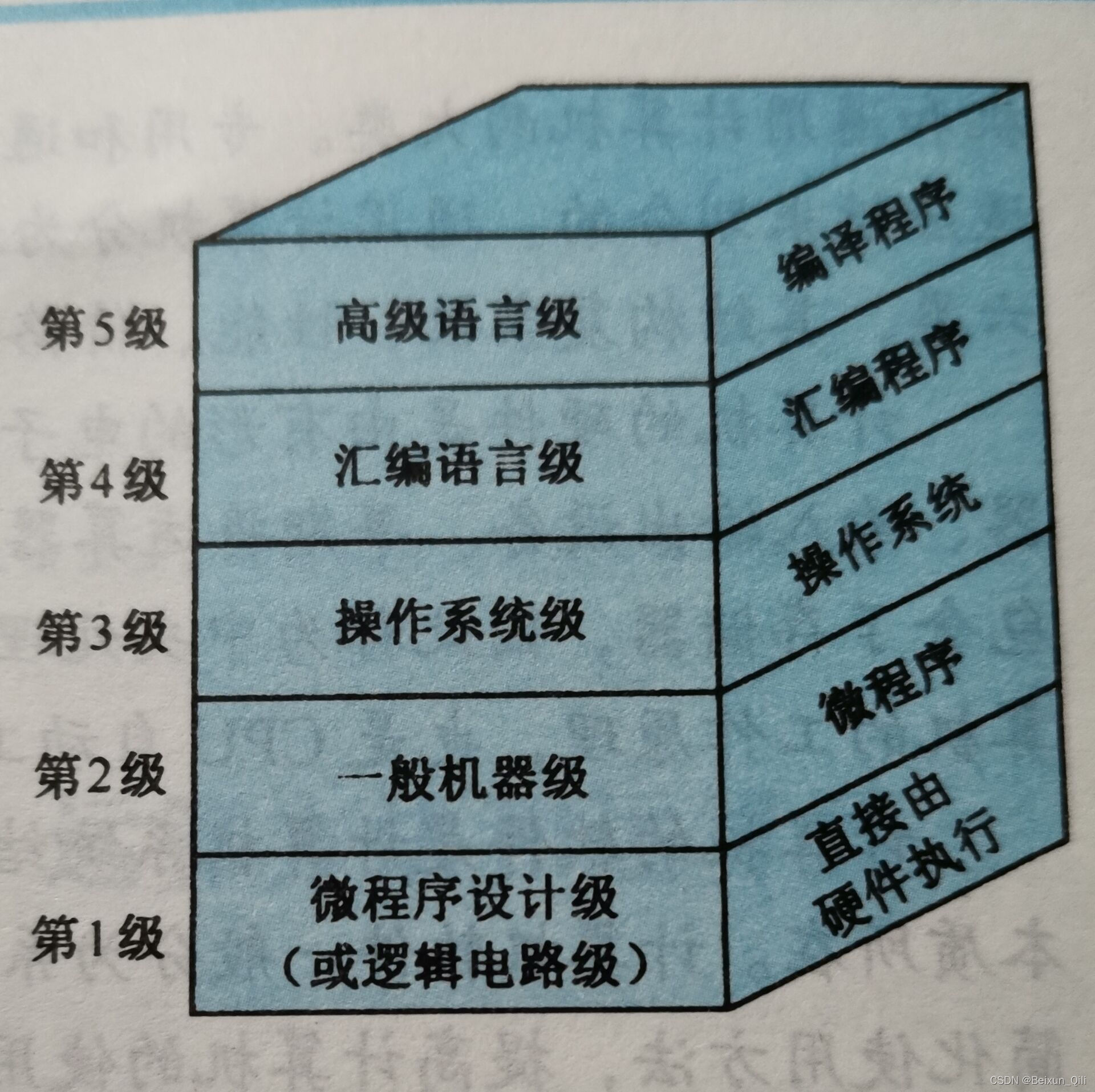

内部结构与带宽计算

DDR的内部构造相当复杂,主要由多个存储阵列和行列解码器等组成。存储阵列是数据的存放区域,而行列解码器则负责确定数据存储的具体位置。这些部件共同协作,确保数据能够迅速存取。在衡量DDR性能时,带宽是一个关键指标。带宽的计算与数据频率、位宽等因素密切相关。

在实际游戏电脑配置中,若想提升整体性能,必须细致考量DDR的带宽。若带宽不够,即便CPU处理能力再强,在应对复杂游戏场景时,数据也无法迅速从DDR传输至CPU。这会导致游戏帧数降低,进而影响游戏体验。

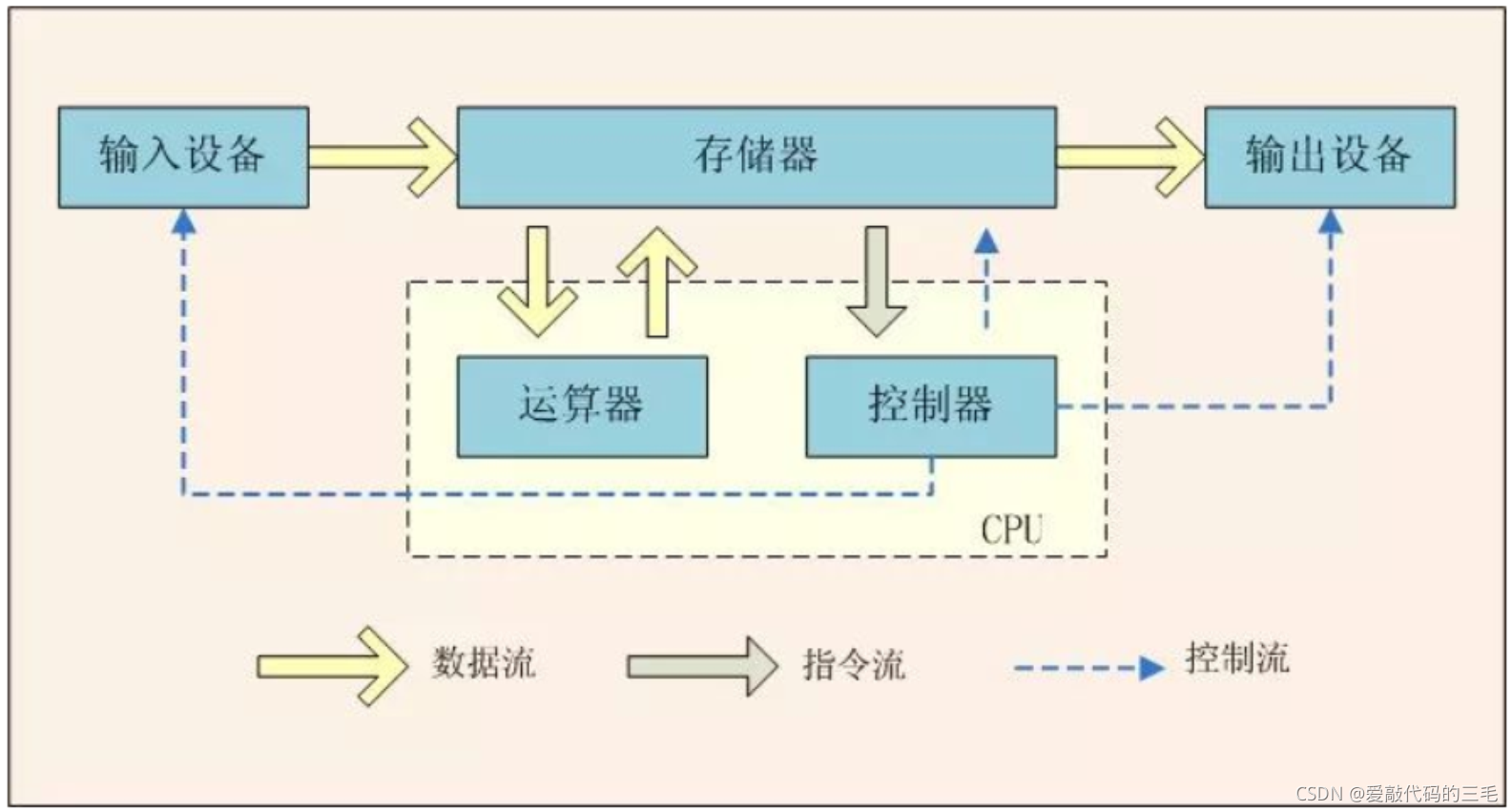

CPU缓存和DDR协同

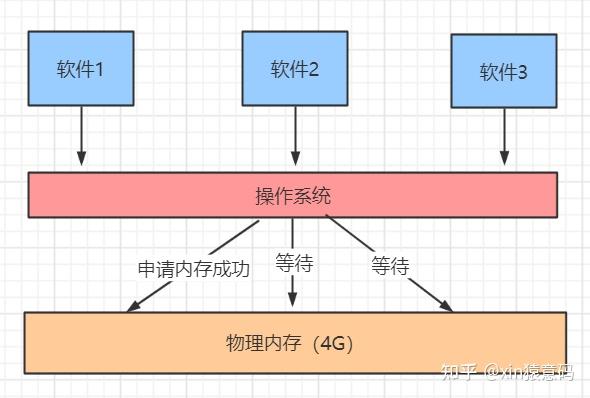

CPU缓存在DDR与CPU的协同工作中扮演着关键角色。通常,CPU具备多层缓存。当CPU需要数据时,它会优先在缓存内搜索。若缓存内无数据,才会转向DDR读取。这种设计旨在缩短CPU等待数据的时间。缓存的存在,恰似一个数据的中转枢纽。

实际上,在多数应用程序的性能优化过程中,CPU缓存与DDR的配合是重点考虑的。若频繁访问的数据能被有效缓存,那么对DDR的读取需求将减少,进而提升整体性能。然而,若缓存策略不当,CPU仍需频繁从DDR获取数据,这会导致效率低下。

DDR频率调整影响

DDR频率的调整对电脑性能的影响是多角度的。提升DDR频率能够加快数据传输的速率。然而,这其中也有一些限制和潜在的风险。首先,DDR频率的提升可能会导致系统稳定性降低。特别是在进行DDR超频操作,也就是提升其工作频率的过程中,很容易出现数据错误的问题。

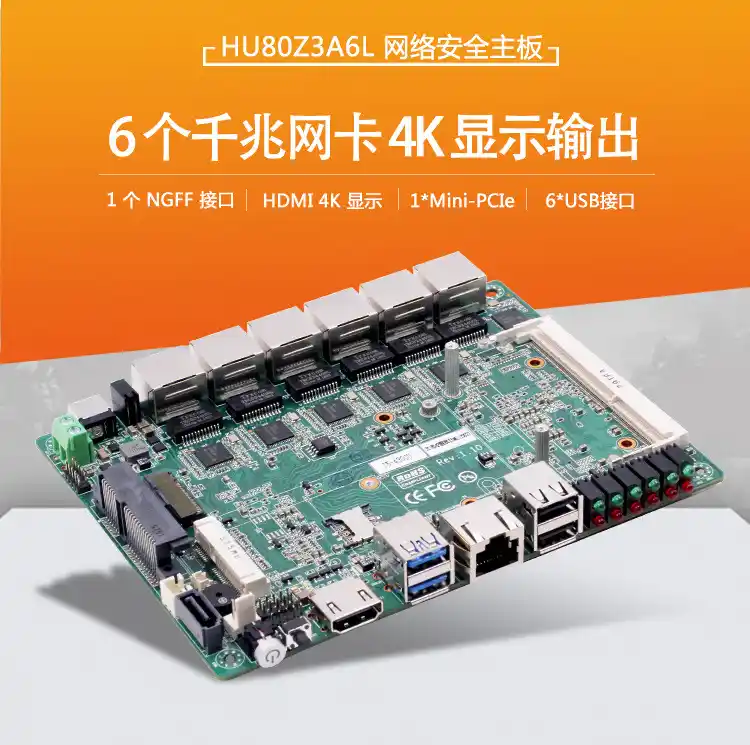

主板的支撑能力同样关键。若主板无法有效支撑高频DDR,硬件稳定性将受影响,甚至可能导致无法正常开机。以老旧主板升级DDR内存为例,若误选高频DDR内存,兼容性问题便可能浮现。

数据传输模式

DDR具备多种数据传输方式,其中包括突发传输模式。在这种模式下,DDR能够连续传输多个数据。这种模式的最大优点是能够迅速完成大量数据的传输任务。一旦命令发出,它便会按顺序连续输出多个数据字。

在实际使用过程中,若数据传输需求显得零散,那么突发传输模式便显现出一定的局限。这种模式传输数据是有序的,这就意味着可能需要等待那些不必要的数据传输完成,才能进行真正需要的数据传输,这无疑会造成时间的浪费。

技术发展趋势

技术不断进步,DDR技术与CPU的配合也在不断优化。不断更新的DDR新版本,为系统带来了更卓越的性能和效率。比如,在人工智能和大数据应用日益增多的未来,对DDR与CPU之间的交互效率提出了更高的要求。

DDR技术有望向更高频率、更大容量和更低能耗的方向演进。然而,它也遭遇了兼容性等挑战。对于电脑爱好者及研发者而言,如何高效运用这项新技术,是一个值得关注的问题。关于DDR与CPU未来的协同发展,你有哪些期待?欢迎踊跃留言、点赞和转发这篇文章。