FPGA的应用领域,DDR(双倍数据率)扮演着至关重要的角色。DDR在增强FPGA的数据处理速度、提升存储效率等方面,具有不可替代的作用。它为FPGA的高效运行提供了坚实的保障。

DDR基础概述

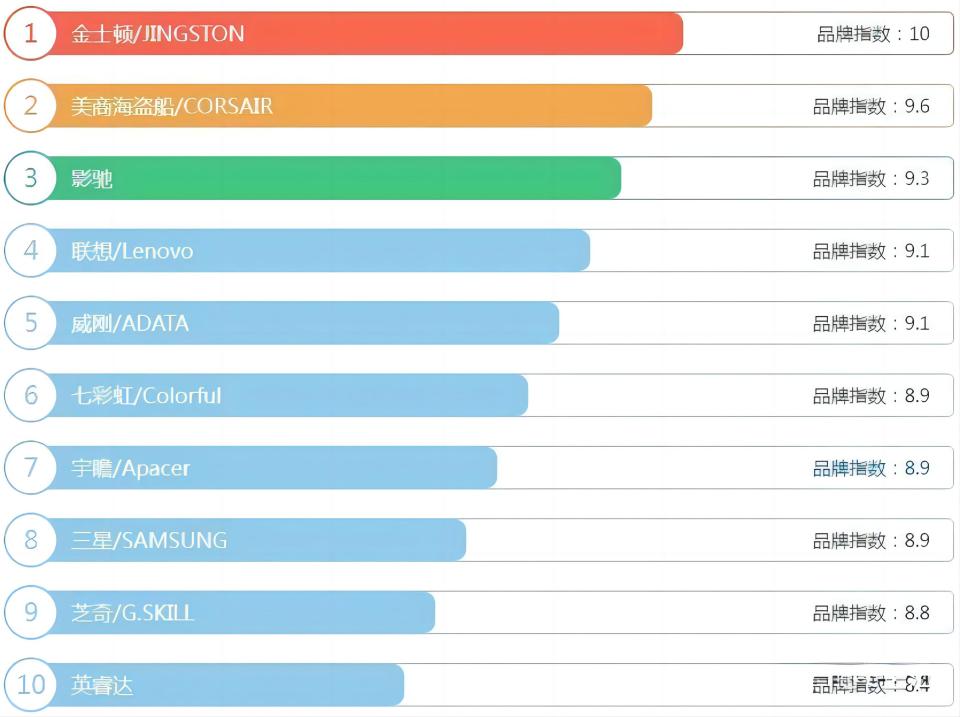

DDR技术允许数据在时钟信号的上升和下降沿同时传输,相较于传统单数据率技术,其传输频率有了显著提高。在FPGA中运用DDR,首先需了解其基本原理。若将FPGA的数据传输过程比喻为一条道路,DDR就好比是拓宽了这条道路,使得数据能够双向迅速流动。此外,DDR类型众多,不同的FPGA开发项目会根据实际需求挑选合适的DDR类型。

FPGA初学者可能觉得DDR这部分比较难懂。这里面包含了许多电路知识的复杂性。不过,一旦掌握了基本原理,对DDR在FPGA中的应用就会更加明了。

DDR在FPGA中的重要性

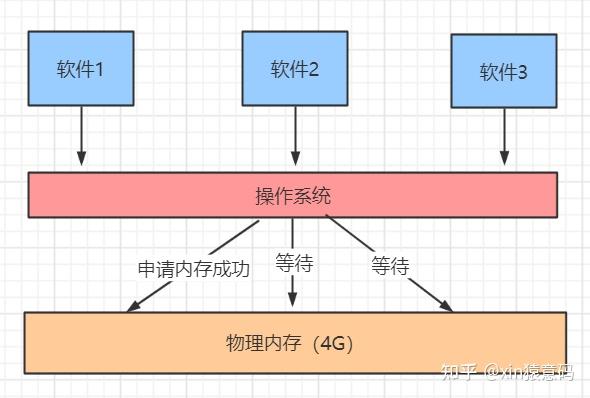

DDR的引入显著提升了FPGA的数据传输带宽。在众多对数据传输要求极高的现代项目中,例如图像和视频处理,带宽不足会导致画面出现卡顿甚至数据丢失。DDR却能有效地避免这些问题,因为它能迅速进行数据的读取与存储。

FPGA在定制开发各种功能方面具有优势,而这离不开DDR的支持。DDR使得FPGA与外部存储或设备之间的数据交换变得既便捷又高效。试想一下,如果没有DDR,FPGA在处理大量高频数据时将会多么吃力,这足以看出DDR的重要性。

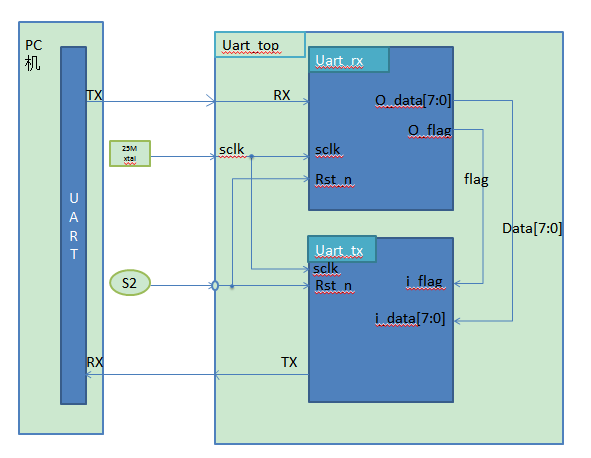

DDR的硬件连接

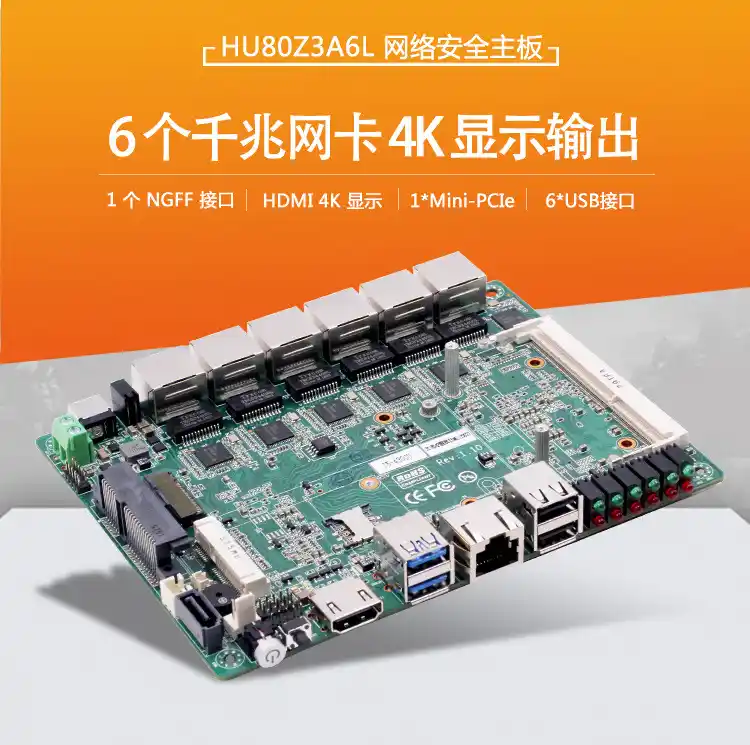

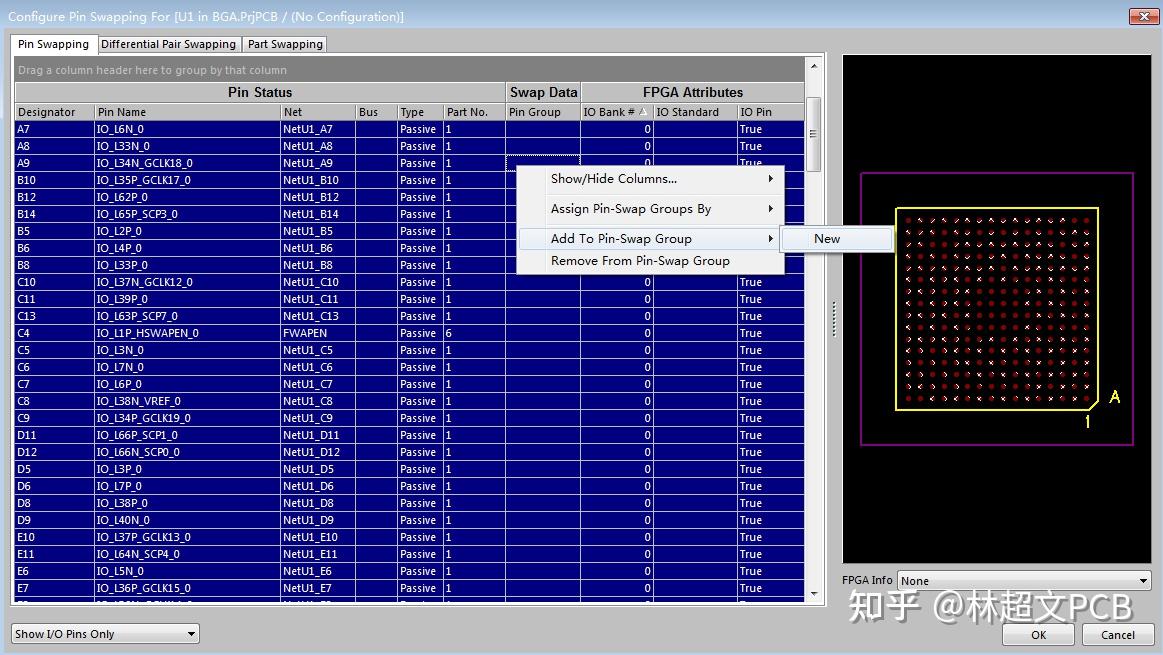

FPGA与DDR的硬件连接既复杂又至关重要。我们必须精心安排引脚的连接方式。不同FPGA芯片的引脚布局各异,与之对应的DDR连接方式也有所不同。以某些FPGA为例,其特定引脚专用于DDR数据读取使能。若连接错误,将无法正常读取数据。

在硬件连接环节,还需注意电平匹配的问题。FPGA与DDR的电平若不匹配,可能导致数据传输失误,甚至损坏硬件。因此,设计硬件连接时,必须精确配置电平转换电路。

DDR的初始化流程

在使用FPGA的DDR之前,初始化步骤是必须的。这包括对DDR控制器的配置过程。DDR控制器需要正确设定各项参数,比如时钟频率和数据宽度等。一旦这些参数设置不当,DDR将无法正常运行。

初始化过程中,还需对若干寄存器进行设置。这些寄存器承载着DDR运行的核心数据,比如读写地址等。每一步都马虎不得,因为它们直接影响到DDR在FPGA系统中的稳定运行和性能表现。

DDR的读写操作

DDR在FPGA上的读写动作必须严格遵循时序规范。写入数据时,必须按照既定时序将数据准确发送至DDR指定的地址。一旦时序出现误差,数据便可能错误地写入不正确的地址,甚至可能完全无法写入。

读取过程与之前相似,FPGA必须精确捕捉DDR的输出时序信号,才能准确读取数据。在项目开发过程中,调试读写操作的时序需要投入大量精力,目的是保证数据的正确传输。

DDR的优化技巧

在FPGA的开发过程中,DDR的优化对提升系统性能至关重要。调整DDR的频率是常见的优化手段。然而,若频率设置过高,超出了硬件的承受极限,便可能引发数据传输的不稳定。因此,寻找一个最佳的平衡点至关重要。

优化DDR的布线至关重要。良好的布线设计能降低信号干扰,进而提升数据传输的精确度和效率。为此,在PCB设计阶段就需要细致规划。

最后,我想请大家谈谈,在使用FPGA的DDR技术过程中,你们遇到了哪些最大的难题?期待大家踊跃点赞、转发,更欢迎在评论区展开讨论。