DDR(双倍数据速率)测试原理包含众多复杂环节,这些环节对于确保DDR内存稳定运行极为关键。这些环节涵盖了地址信号、数据信号、时钟信号等各方面的测试逻辑,涉及丰富的专业知识。

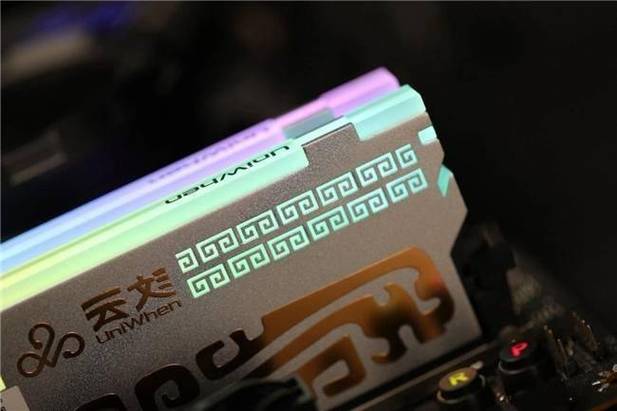

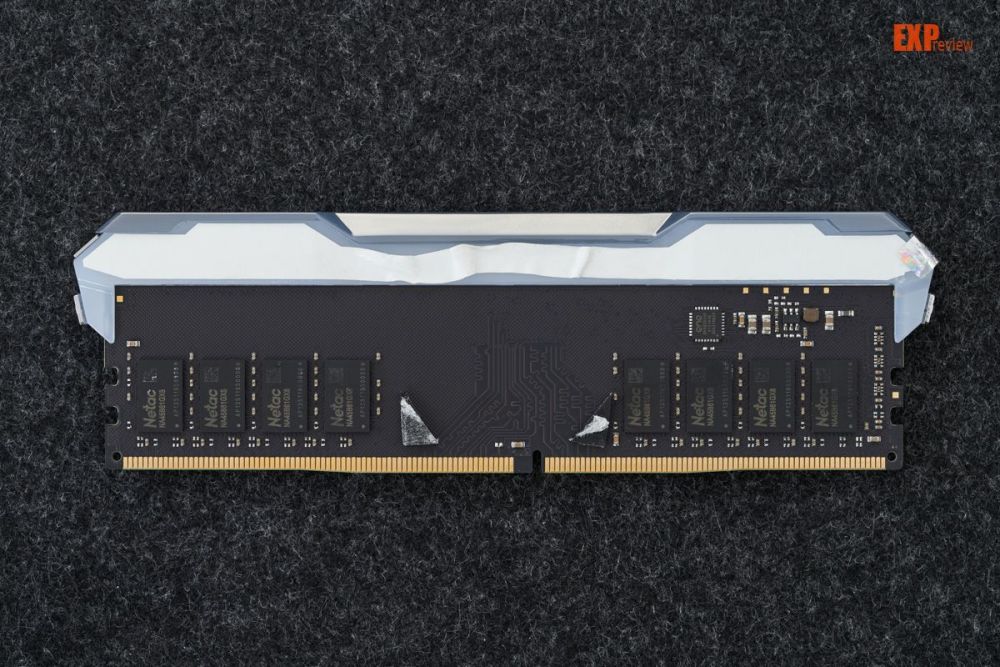

DDR基本结构

DDR的结构设计非常巧妙。从物理角度来看,它拥有众多存储单元矩阵。每个存储单元都配有独立的行列地址,确保数据的准确存储和读取。这样的结构,宛如精密机械表的内部构造,运作精准。此外,DDR与普通存储结构的不同之处在于,它能够实现双倍速率的数据传输。这一功能是通过特殊的底层电路和信号控制逻辑来实现的。这就好比给汽车换上了高性能发动机,让数据传输速度大大提升。

这个结构在DDR的实际应用中极为重要。因为现在,诸如电脑、手机等众多电子产品,对数据的快速读写有着极高的要求。DDR的这种设计,恰好能够高效地满足这些需求。否则,数据传输的缓慢将会拖累整个设备的运行速度。

地址信号测试

地址信号的检测是DDR测试原理中的关键步骤。首先,必须保证地址信号的完整性。只有精确的地址信号,才能确保数据能够准确无误地被存储到相应的存储单元。这就像快递的地址必须准确无误,才能将包裹送达指定地点。一旦地址信号出现错误,数据就可能被错误地存储。

需要检测地址信号的时序问题。这涉及到它与其它信号之间的配合是否得当。就好比交响乐团中各种乐器,必须在恰当的时刻发声,才能演奏出美妙的乐章。若地址信号的时序不协调,就可能引发数据读写错误等问题。

数据信号的测试极为重要。首先,必须确保数据信号的正确性。数据必须按照既定的格式进行传输,这些数据最终会被用于多种用途,例如在电脑中进行运算和显示等操作。一旦数据出现错误,就如同建筑根基不稳,将引发一系列后续问题。

数据信号的稳定性同样重要。在多种环境变化中,比如温度波动、电磁干扰等,数据信号必须保持稳定。这就像长跑运动员需要保持体力,才能跑完全程。若数据信号不稳定,可能会出现数据丢失或乱码等问题。

时钟信号的影响

时钟信号在DDR中扮演着指挥家的角色,掌控着同步的节奏。从某个角度看,时钟信号的频率设定至关重要。高频率的时钟信号可以加快数据传输速度,但同时也对电路的性能提出了更高要求。以高端游戏电脑为例,高频率的时钟信号有助于电脑快速处理大量游戏数据。

另一方面,我们要关注时钟信号的相位关系。只有相位适宜,各信号才能协同运作。这就像在团队协作中,成员之间需要保持恰当的站位一样。一旦相位出现偏差,数据读写就会陷入混乱。

测试的流程顺序

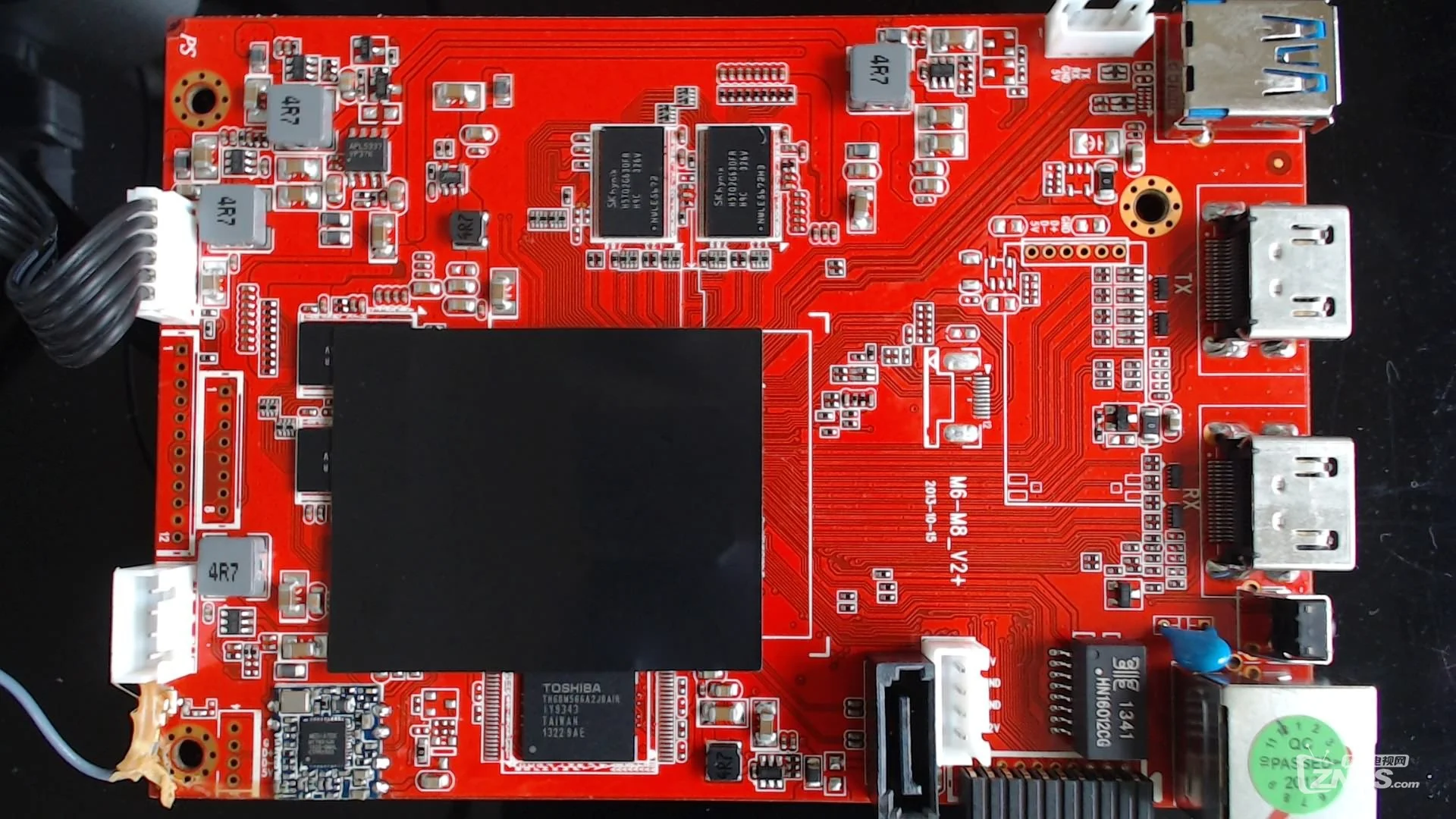

DDR测试的流程是有一定顺序的。首先,必须检查硬件连接是否准确无误,这是至关重要的第一步。一旦硬件连接出现错误,接下来的测试就无法顺利进行。这就像是没有铺设好的铁轨,却要让火车行驶,那是不可能实现的。

信号层面的测试随后展开,先从地址信号入手,接着是数据信号,最后是时钟信号,如此逐一进行。这一测试流程是依据信号在DDR运行中的关键作用和逻辑顺序来安排的。就好比装修房屋,得先完成水电安装的基础工作,之后才能进行室内装饰等后续步骤。

测试工具及使用

DDR测试有众多专业工具。比如,示波器能帮助我们观察信号的波形等细节。借助示波器,我们可以直观地检查时钟信号、数据信号等波形是否正常。这就像医生用听诊器听心跳来评估患者健康状况一样。

测试工具的参数设置必须准确无误。不同的DDR产品对测试参数的要求各异。一旦设置错误,测试结果将不准确,就如同戴错了眼镜,看世界都会变得模糊不清。

各位读者,DDR测试原理中,哪个环节最容易被大家忽略?不妨在评论区留言讨论一番。若您觉得这篇文章不错,别忘了点赞和分享。