DDR等长设计在DDR布线中扮演着至关重要的角色。这一设计要求,各种信号传输线在电气特性上必须保持一致。这样的设计对于确保内存稳定运行至关重要。打个比方,这就如同要求一群运动员既要同时起跑,又要同时到达终点,这是维护整体协调性的关键设计考虑。

DDR等长设计的意义

DDR等长设计的主要目的是为了保障信号的同步性。在DDR的数据传输过程中,众多信号往往是同时进行发送和接收的。一旦传输线的长度存在较大差异,信号到达的时间就会产生不一致。这就像班级里的同学们在进行接力比赛,如果起跑的时间不统一,比赛就会变得混乱不堪。这种信号的同步问题可能会引起数据错误,甚至导致系统不稳定。

同时,从电气性能的角度来看,等长的设计有助于降低信号反射。当信号在传输过程中遭遇传输线长度突然变化,或者传输线的特性阻抗不匹配时,就会产生反射。然而,采用等长设计,可以维持传输线的一致性,有效减少反射的发生,确保数据传输的稳定性。这就像确保公路平坦且畅通无阻,使得跑车能够顺利高速行驶。

影响等长设计的因素

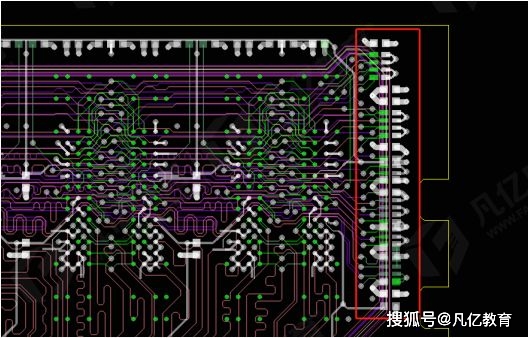

电路板布局至关重要。合理的布局是等长设计的基础。举例来说,如果DDR芯片周围有其他元件阻挡,布线就会变得困难。传输线可能会出现锯齿状或者曲折布线的情况。这就像在一片整齐的田地里突然冒出几块大石头,影响了种田的布局。

此外,布线空间也是一个限制因素。电路板若尺寸偏小或元件过于密集,DDR的布线空间就会变得十分有限。在这样的条件下,实现等长设计会变得极其困难。这就像是在一个狭小的空间内摆放众多家具,同时还要确保电线排列整齐、长度一致,难度之大不言而喻。

等长设计中的公差范围

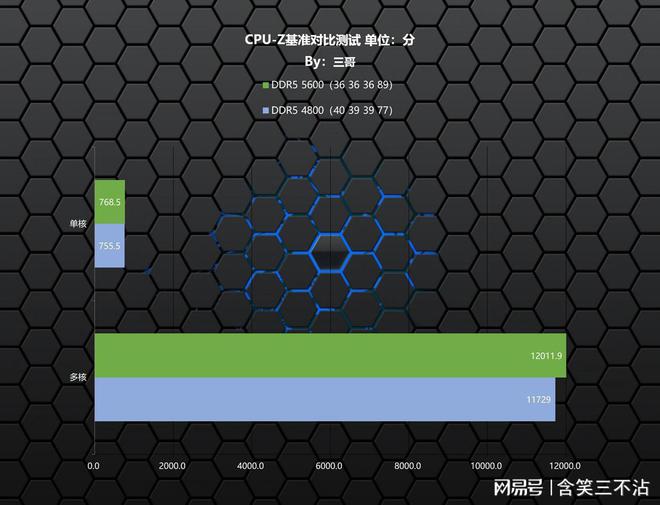

等长设计允许存在一定误差。这种误差与DDR的工作频率密切相关。DDR工作在低频时,信号的波长较长,对传输线长度的不一致容忍度较高。这好比慢跑时,交接棒的距离略有波动,影响并不大。

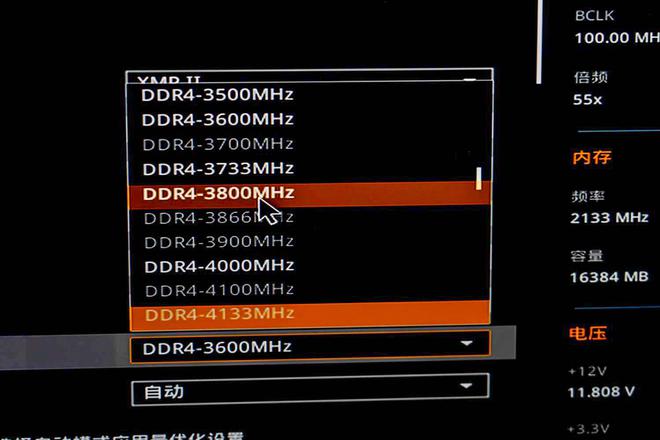

DDR在高频工作时,信号波长会变短,因此对公差的控制必须更加严格。此时,哪怕是极小的等长差异也可能引发严重问题。这就像在赛车比赛中,哪怕是一瞬间的失误,也可能导致原本领先的选手失去优势,从而改变整个比赛的结果。

实现等长设计的方法

蛇形布线是一种可行的选择。它通过使线路弯曲来调整传输线的长度,从而使各条线路的长度大致相同。这就像拼图一样,通过巧妙地改变小块拼图的形状,最终完成整个图案的拼接。

另一方面,关键在于合理的分层布线。通过电路板的多层布局,我们能够依据每层的特性,科学地规划出路径,从而实现等长设计。这就像在大楼中,巧妙地利用不同楼层空间,合理安排通道,以达到最佳的通行效果。

等长设计在实际中的应用案例

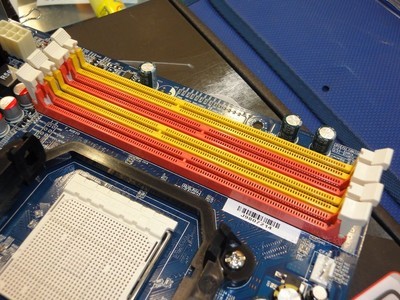

电脑主板设计中,DDR等长设计被广泛应用。高性能主板制造商特别重视DDR的等长设计。这种设计能够提升电脑的整体性能,降低系统崩溃和数据错误的发生几率。就好比为高性能跑车精心打造了一块既平坦又整齐的赛道。

在服务器内存模块的设计中,DDR等长设计至关重要。服务器需持续稳定运行,处理繁重的数据业务。若等长设计不周全,可能导致数据存储错误或服务器崩溃。这就像铁路运输,轨道一旦出现问题,列车就可能脱轨。

等长设计的发展趋势

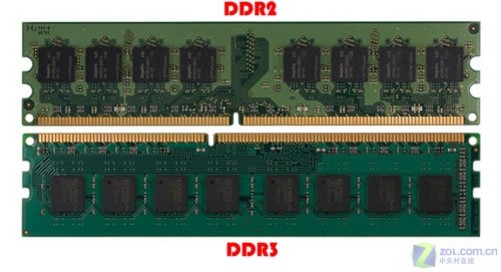

DDR技术不断进步,对等长设计的要求也在不断提升。工作频率和传输速度的提升,使得等长设计需要更加精密。这就像运动员追求更快的速度,对训练场地的设计标准也随之提高。

在PCB小型化趋势日益明显的当下,要在更狭窄的空间里实现DDR等长设计,这对行业来说是一项重大挑战。这情形就如同在一个不断变小的盒子里,试图装入更多、更精致的东西。

在职场中,你是否曾遭遇过DDR这类长设计带来的挑战?期待各位朋友为这篇文章点赞并转发,同时,欢迎大家在评论区留言交流。