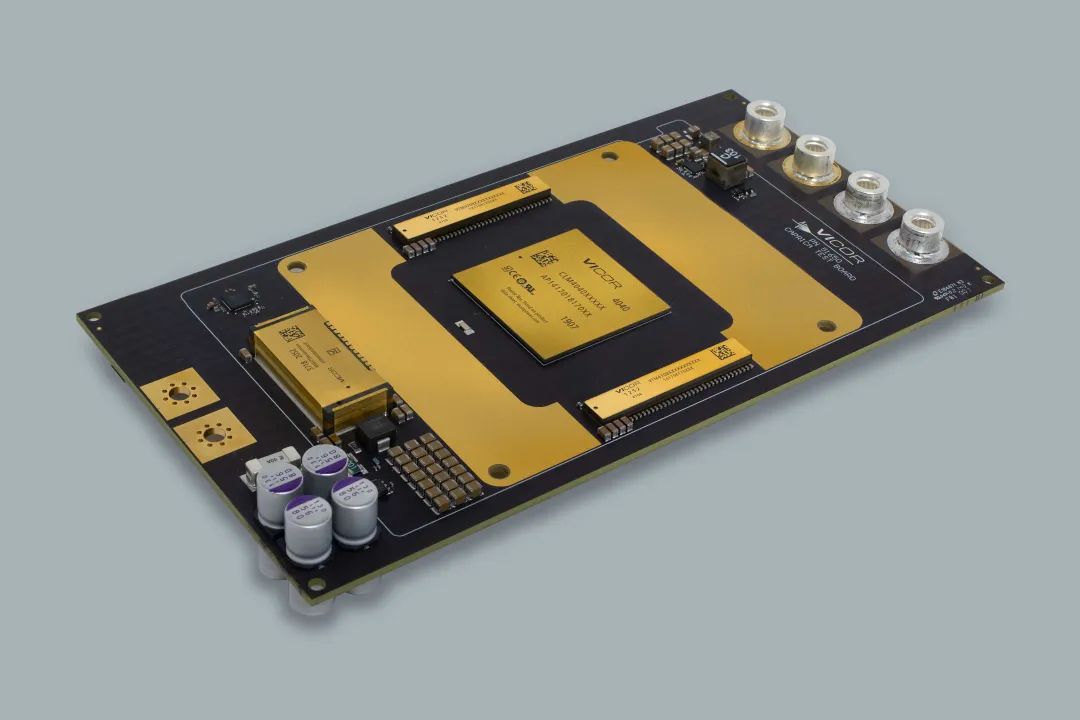

在PCB(印刷电路板)设计过程中,DDR(双倍数据率)相关内容的绘制至关重要。DDR在现代电子设备中扮演着高速数据存储与传输的关键角色。DDR的PCB绘制需考虑众多因素,包括但不限于信号完整性、布线规则等,这些都是我们必须细致思考的问题。

理解DDR原理

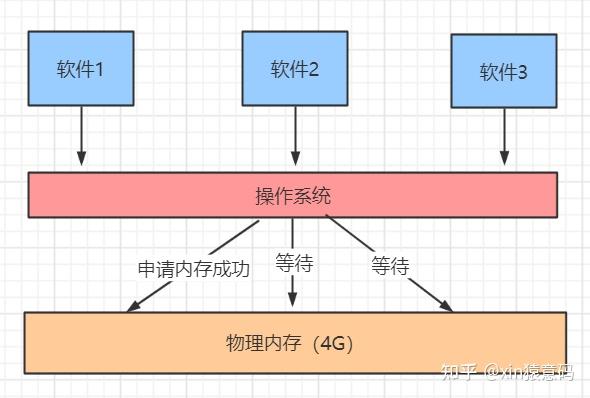

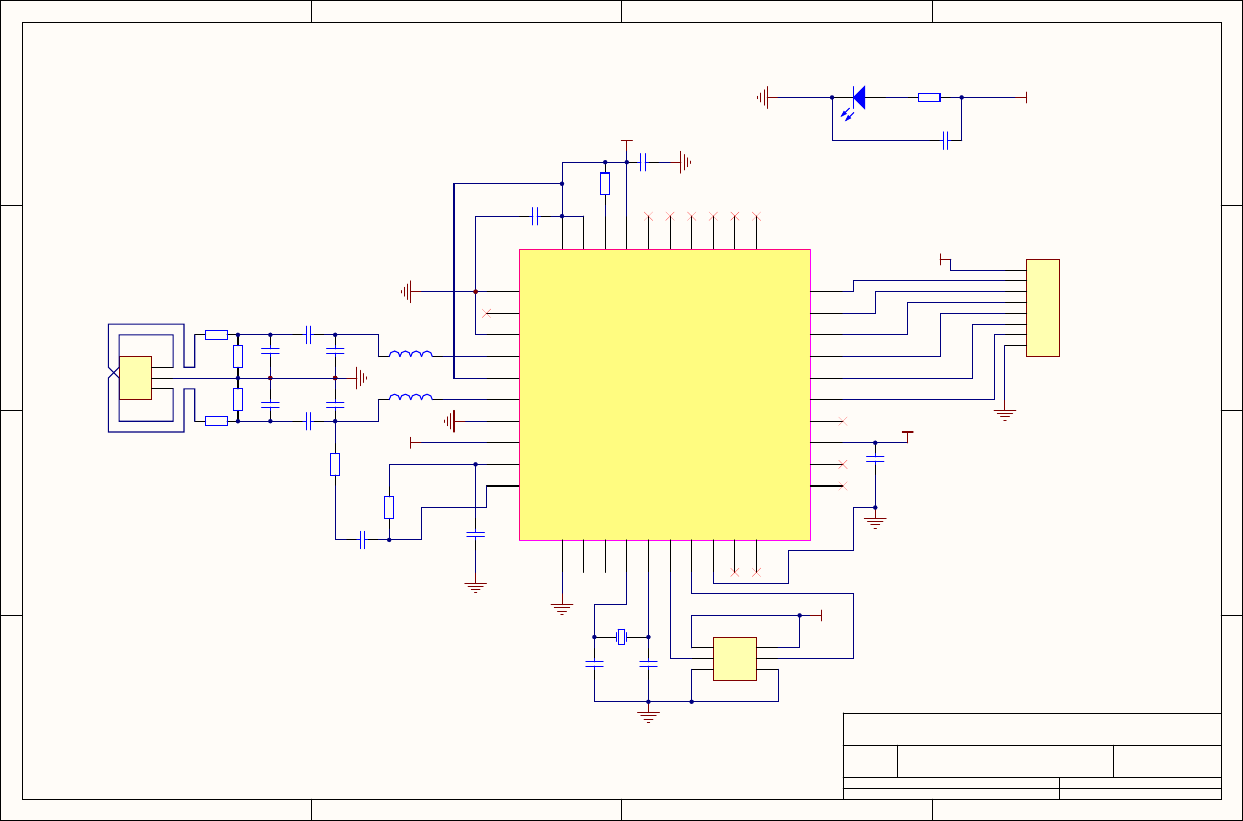

理解DDR的工作原理对于PCB绘图至关重要。DDR利用高速时钟信号实现数据传输速率的提升,达到双倍。这要求我们在版图设计上准确反映复杂的读写操作逻辑,如地址线、数据线等信号布局。传输速度越快,对线路规划的精准度要求越高。掌握DDR原理有助于更准确地确定PCB设计中各模块的布局位置。这样做可以避免因原理理解不足导致的信号传输错误等问题。

DDR的预取机制是原理中的关键环节。预取的大小不同,会导致数据传输模式有所区别。在PCB绘图过程中,我们必须考虑到这一点,合理规划相关线路。这样,才能确保在不同预取模式下,数据能够稳定传输。否则,简单的线路问题可能会导致数据加载出错。

信号完整性要求

DDR数据传输速度极快,因此信号完整性显得极为关键。首先,必须严格把控信号的时序。任何微小的时序偏差都可能引发数据读写错误。以数据线的长度为例,它必须精确匹配,否则同步性会受到影响,导致数据读取时间的偏差。在绘图过程中,必须对布线的长度进行精确的计算和细致的调整。

信号质量必须保持优良。这要求我们采取有效措施,比如控制好信号的反射噪声。布线时,应尽量避免形成直角,而是尽量使用45度角走线,以此减少信号反射。若信号质量不佳,数据传输时便可能出现误码,进而影响整个系统的正常运行。

布局要点

DDR在PCB上的排布必须依照既定规范。总体来看,它应与周边的电路模块保持恰当的相对位置。比如,与CPU这样的数据处理中心模块,距离不宜太远。若距离太远,可能会导致传输延迟增加。

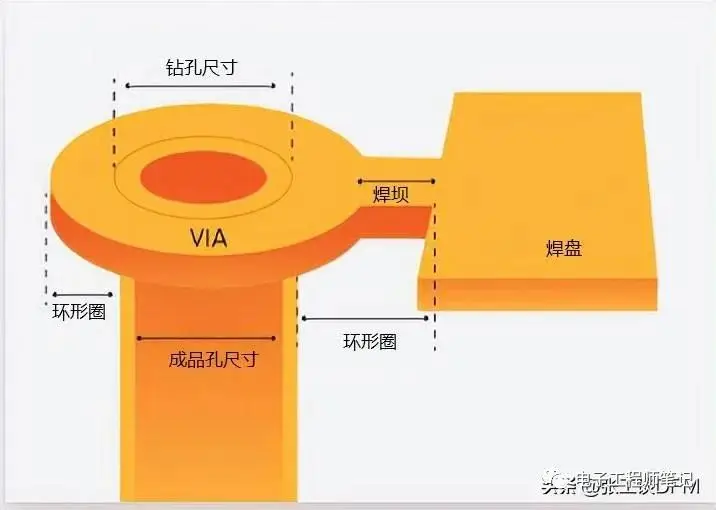

DDR芯片的内部电路布局讲究门道。特别是电源引脚和地引脚的布置,至关重要。它们需要既合理分离,又便于形成低阻抗的供电回路。毕竟,电源供应的稳定性直接影响到DDR工作的稳定性。若布局不合理,还可能引发电源噪声对信号的干扰。

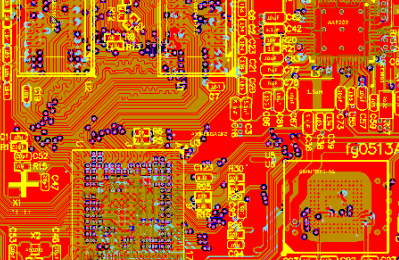

布线规则

布线在DDR的PCB设计中至关重要。首先,数据线和时钟线的布线必须确保等长。正如之前所述,为了保证时序的准确性,任何微小的长度差异都可能导致时序偏差。一般会设定一个公差范围,比如±10mil。

布线宽度与间距同样不容忽视。根据不同的DDR标准,布线宽度和间距的最小值都有明确规定。在PCB设计时,必须严格遵守这些规定,以防出现信号干扰或串扰等问题。以DDR3标准为例,若布线宽度设置得过窄,可能会导致电阻增大,进而影响信号传输的质量。

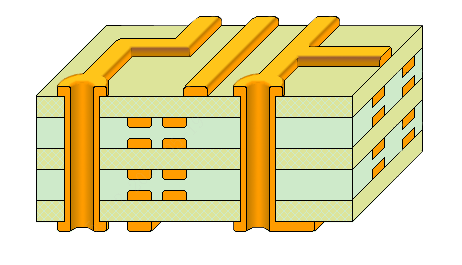

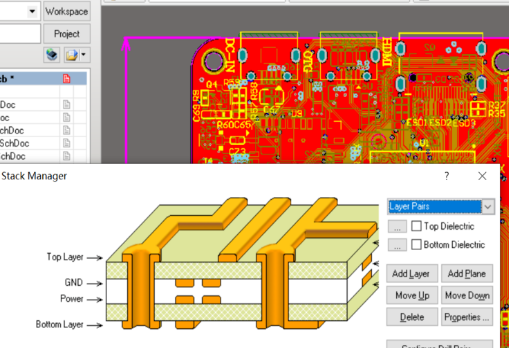

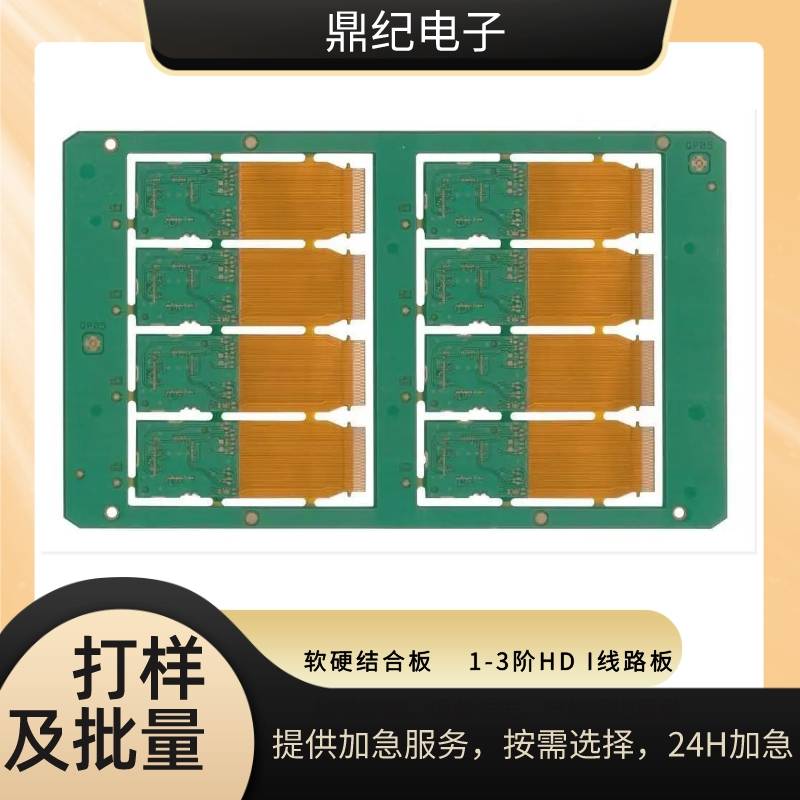

层的规划

在DDR的PCB绘图过程中,层的规划扮演着至关重要的角色。信号的层数需谨慎挑选,多层板能有效隔离信号,不过其成本也相对较高。尤其在小型电子设备的设计中,若层数选择过多,不仅会提升成本,还会增大体积,因此必须首先进行权衡。

内层和外层的信号规划各有其重点。外层信号更容易受到外部干扰的影响,比如时钟信号这样的关键信号,若布置在外层,就需要采取更为严格的屏蔽措施。相较之下,内层信号则相对稳定,但散热条件却相对较差。

电源与地的处理

电源与地的处理对DDR的工作稳定性至关重要。电源网络需精心设计,合理规划电源通道的走向,以确保DDR能够稳定供电。

接地问题,需选用合适的接地方法,比如单点接地或多点接地,具体需根据实际情况来定。接地做得好,能有效降低噪音干扰。比如在处理大电流DDR工作时,单点接地可能会引发地弹等问题,这时多点接地就显得更为适宜。

在绘制DDR的PCB图过程中,你是否曾因某个小细节而不得不重新设计整个方案?若你觉得这篇文章对你有所帮助,不妨点个赞并分享出去。