DDR芯片里的DQS信号至关重要。这个信号主要用于DDR内存的运作中,同步数据传输。简言之,DQS能确保数据在内存与处理器等部件间准确无误地传递。这一点对于计算机系统的高效稳定运行至关重要。

起源与发展

DDR芯片技术持续进步,DQS的诞生亦伴随DDR技术的演变而来。起初,内存技术传输数据速度较慢,对同步信号的需求并不迫切。然而,随着计算机性能需求的提升,DDR芯片的传输速度日益加快,数据传输的稳定性面临挑战。正是在这样的背景下,DQS应运而生。它能在读写过程中精确地定位时钟周期,从而避免数据传输的混乱。此举提升了内存读写数据的效率,让计算机处理信息更加高效。

在DDR芯片的发展过程中,每次升级换代都伴随着DQS技术的进步。通过调整DQS的频率和时序等关键参数,DDR芯片得以在更高的数据传输速度中保持稳定和可靠。

技术原理

DQS的工作原理是依托于时钟信号。在进行DDR内存的读写操作时,DQS与时钟信号共同工作。数据的传输并非独立进行,它需要借助一个参考信号来确认数据何时生效。DQS便承担了这一职责。以读取数据为例,当DQS信号抵达接收端,接收端会根据DQS信号来判断此刻接收到的数据是否为有效数据。至于写入数据,DQS会将数据的写入时刻与时钟周期进行精确对应。

DQS信号若出现偏差,便可能引发数据传输错误。比如,数据可能因DQS失调而提前或延迟被认定为有效,进而直接导致传输错误,这可能是单个数据位的错误,也可能是连续数据的错误,从而严重影响系统的稳定与数据准确性。

功能优势

DQS为DDR芯片增添了显著的数据准确性优势。在DDR芯片高速运行时,若缺乏DQS的精准数据同步,数据传输极可能产生众多错误。而且,它还能有效提高内存带宽的使用效率。借助精确的时钟和数据同步,单位时间内能够传输更多的有效数据,这对于提升计算机系统的整体性能至关重要。

高端计算机应用,诸如大型服务器与图形工作站,对DQS的依赖至关重要,因为它是确保系统稳定高效运行的必要条件。在这些应用中,内存不仅要处理庞大的数据量,还要保证数据传输的准确性,不容许有丝毫误差。DQS恰好能够满足这些严格的要求,因而成为DDR芯片在高端领域得以应用的关键保障。

面临挑战

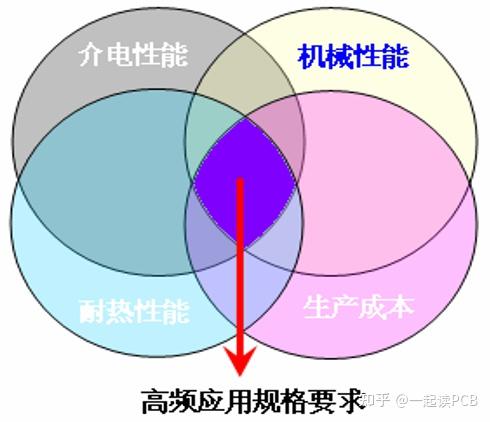

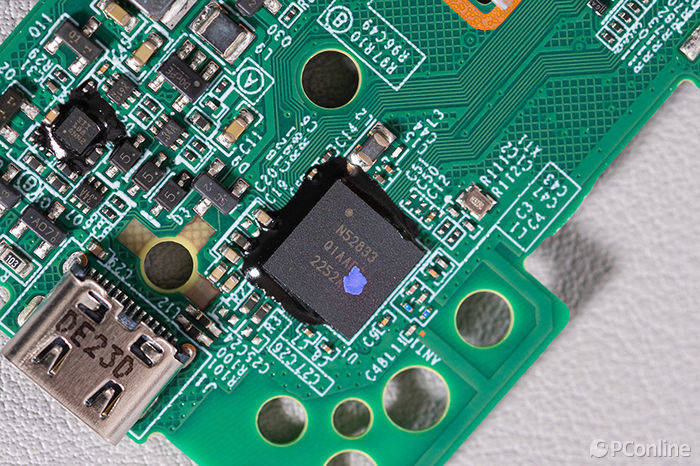

在实际使用中,DQS遭遇了不少难题。其中,信号完整性问题尤为突出。DDR芯片的数据传输速度持续提高,DQS信号在传输途中很容易受到干扰。这种干扰可能源于电磁辐射、电路板设计不合理等多方面原因。比如,电路板上过长的走线或不当的布线设计,都可能导致DQS信号出现反射、衰减等问题。

实现DQS与其它相关信号的精确时序对齐并不简单。因为不同的DDR芯片制造商可能遵循各自的设计规范,这无疑让完美时序匹配变得更加困难。而且,这种时序上的不吻合还可能引发数据传输错误。

优化方案

为了解决DQS信号完整性问题,电路板布局的优化是关键。比如,可以缩短DQS信号的走线长度,并且合理安排与电源线、地线等的位置。这样做可以降低电磁干扰。另外,采取更有效的信号屏蔽措施,同样有助于保护DQS信号免受外界干扰。

在时序匹配上,芯片生产商可确立统一的标准或规范,以便各类DDR芯片在与其它部件连接时,能更简便地达到时序的精确对应。系统设计师们也能选用更高级的时序调整电路,对DQS的时序进行细微调整,以适配不同的DDR芯片。

对消费者影响

DQS,虽然对普通消费者而言是一个较为基础的技术术语,却与他们的使用感受紧密相连。当DQS功能运行正常,消费者在使用电脑时能体验到更顺滑的程序运行和更高效的数据处理速度。反之,一旦DQS出现故障,电脑可能会频繁出现死机、软件出错等问题。

你是否留意过,你电脑出现的某些问题,或许与DQS有关联?若觉得这篇文章对你有帮助,不妨点赞、分享和评论。