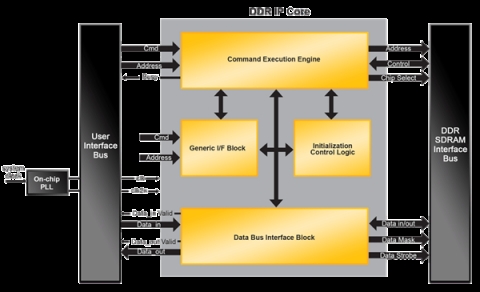

ddr总线时钟在计算机存储系统中扮演着至关重要的角色。作为内存数据传输的关键参数,它直接关系到内存与处理器间的数据交换效率,进而影响整个计算机系统的性能表现。

基本概念理解

ddr总线时钟,顾名思义,指的是ddr总线上的时钟信号。它就如同一个有规律的节拍器,有条不紊地调控着数据的流动。在电路的实际运作中,这个时钟信号的频率直接决定了数据传输的周期。首先,它的计量单位是Hz,代表每秒钟的时钟周期次数。其次,这个时钟信号的稳定性同样至关重要,一旦不稳定,便可能引发数据传输的错误。

在日常使用的电脑里,这个概念对众多操作有影响。启动大型软件或处理多项任务时,ddrbusclock便会介入到数据的快速传输环节。若该参数设置过低,程序可能会出现响应迟缓的情况。

对性能的影响力

较高的DDR总线时钟能提高内存数据的传输速度。这就像为数据开辟了一条高速通道,使得数据能在内存与处理器间更迅速地流动。比如在玩游戏时,高速的DDR总线时钟能让游戏场景加载更快,画面切换更加顺畅。

此外,这也对多任务处理能力产生了影响。当同时运行多个程序时,若ddrbusclock的设置得当,程序间的数据交换便会更加快捷,系统不会出现卡顿现象。相反,若ddrbusclock的频率偏低,进行多任务处理时,电脑的反应可能会显得有些迟缓。

调整和优化

调节DDR总线时钟是增强系统性能的一个途径。一种操作方法是借助BIOS进行配置。然而,这种操作需格外小心,不恰当的调整可能会引发系统不稳定。对于熟悉操作的用户新手,可以尝试逐渐提升DDR总线时钟的频率,以此来检验性能的改善。

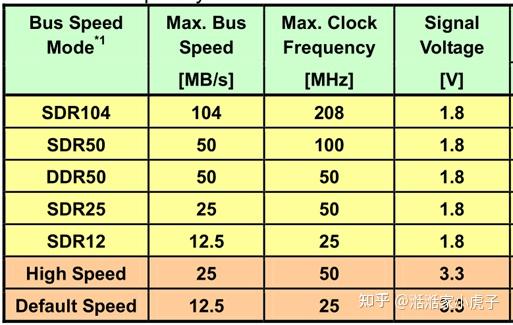

同时,不同的内存模块对DDR总线时钟的支持范围各不相同。知晓内存的具体规格,有助于我们更合理地调整DDR总线时钟。以某些高端内存模块为例,它们能够支持更高的DDR总线时钟频率,从而充分发挥其性能上的优势。

硬件兼容性

ddr总线时钟与主板的关系十分紧密。主板上的芯片组对ddr总线时钟的兼容性存在一定限制。不同型号的主板所能支持的ddr总线时钟频率范围各异。若主板无法支持过高的ddr总线时钟频率,即便内存具备这一性能,也无法实现正常工作。

此外,CPU与内存控制器之间也存在着兼容性的挑战。内存控制器必须与ddr总线时钟保持一致。若两者兼容性不佳,数据传输效果将受到影响,甚至可能引发系统崩溃等严重问题。

常见问题及解决

ddrbusclock的问题中,系统不稳定的情况时常发生。一旦提高ddrbusclock的频率,系统就可能出现蓝屏或死机等问题。这时,我们可能需要考虑降低频率。

还有一个问题是数据传输出现了差错。这可能是由于时钟信号受到了干扰,或者是因为硬件出现了故障。为了解决这个问题,我们可以检查硬件的连接是否正常,更换损坏的硬件,或者对电路布局进行优化。

未来发展趋势

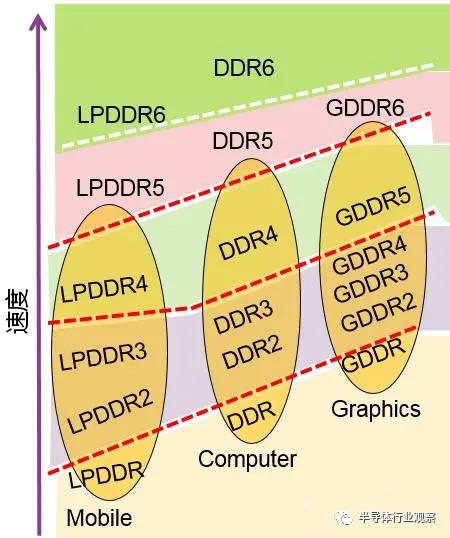

技术不断进步,ddr总线时钟的频率有望持续提升。这主要是因为计算机对内存性能的要求日益增强。比如在大数据分析和人工智能等应用领域,更高的ddr总线时钟频率能显著提高数据传输和计算速度。

同时,新技术有望优化DDR总线时钟与硬件间的兼容性。这样,在提高频率的同时,系统的稳定性也不会受到太大的影响。

我想请教各位读者,在调整电脑ddr总线时钟的过程中,有没有什么特别难忘的经历?期待大家的点赞和分享这篇文章。