DDR(双倍数据率同步动态随机存取存储器)的引脚分布颇为复杂,却至关重要。这一分布影响着DDR模块与其它设备的连接,对于理解DDR的工作机制以及其在不同电路设计中的应用,具有决定性的影响。

主板插座与引脚对应

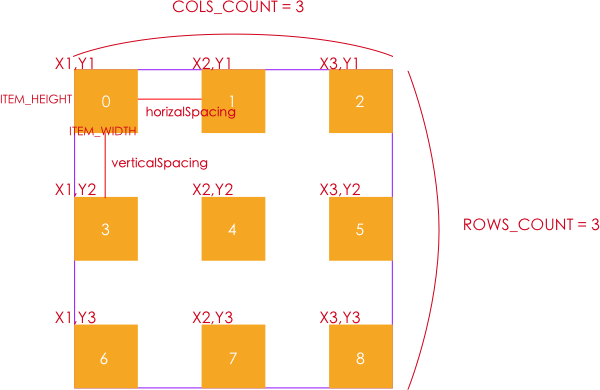

主板上的DDR插座有特定设计,不同版本的DDR插座在引脚布局上有所差异。以DDR3插座为例,其引脚排列是经过周密设计的。从功能区域来看,有负责供电的引脚区域,这些引脚为DDR芯片提供稳定的电源,确保其正常运作。若电源引脚布局不合理或出现故障,DDR将无法正常工作。此外,还有地址引脚区域,地址引脚用于确定读写DDR的特定存储单元,其精确布局确保每个存储单元都能被准确无误地定位。

DDR插座的设计标准相当严格。主板制造商必须严格遵守这些规范进行生产。若不如此,将可能引发与DDR内存的兼容问题。特别是那些仿造的主板,若不按照引脚分布的标准来制作,使用DDR内存后很可能会频繁出现蓝屏和死机的情况。

数据引脚布局

DDR的数据引脚布局依据高速信号传输的规则。这些数据引脚通常以成对的形式出现,其目的是为了进行差分信号传输。差分信号传输的一大优点是抗干扰能力强。在布置数据引脚时,会考虑到传输线等长等设计的要求。以PCB(印刷电路板)设计为例,若数据引脚对应的走线长度不等,就可能会造成传输时延的不同,进而可能导致数据传输出错。

同时,在数据引脚周围,通常都会布置专门的接地保护引脚。这样的设计能有效阻挡外界干扰,确保数据引脚在传输过程中的稳定。以高密度PCB设计为例,我们必须特别关注接地保护引脚的合理布局,以防信号串扰问题的发生。

时钟引脚的位置

时钟引脚在DDR引脚分布中的位置极为关键。时钟信号,作为DDR运行的节拍器,其重要性不言而喻。通常,时钟引脚位于中心区域,或是紧邻关键控制引脚的周边。这样的布局旨在确保时钟信号能以最短的距离和最少的延迟,传递至所需的所有部分。一旦时钟引脚位置不恰当,便可能导致时钟信号的偏差。

时钟引脚附近通常配有去耦电容引脚。这些去耦电容引脚的主要功能是过滤时钟信号,从而提高信号的纯净度和稳定性。若布局不当,可能会导致时钟信号中的杂波增加,进而影响DDR的工作频率和稳定性。

控制引脚分布

在DDR中,控制引脚扮演着指挥交通的关键角色。例如,片选信号引脚,它决定了DDR芯片是否被选中执行操作。在布置这个引脚时,必须考虑到它与其它相关引脚的协作是否便利,比如,读写控制引脚的布线不能与之冲突,同时信号传递的路径应尽量缩短。

有行地址选通和列地址选通等控制引脚存在。这些引脚的布局会影响到DDR存储单元的寻址速度与精确度。若控制引脚的排列或位置不当,将导致存储单元访问延迟上升。在频繁进行内存读写操作的环境中,这种延迟可能会导致整个系统性能大幅降低。

电源相关引脚分布

电源相关引脚的布局旨在保障DDR获得稳定的电力供应。供电引脚的设计会依据DDR的功率需求进行合理安排。对于功率较高的DDR模块,需要配置更多的电源引脚以确保电流供应充足。此外,电源引脚还需与接地引脚构成良好回路,从而确保电能传输的高效性。

电源引脚周边通常都会进行电磁兼容性的优化设计。这包括设置屏蔽罩或其他抗电磁干扰措施。因为电路中的电磁干扰若影响到电源引脚,便可能引发DDR电压波动。而这种波动又可能引起数据存储或读取的错误。

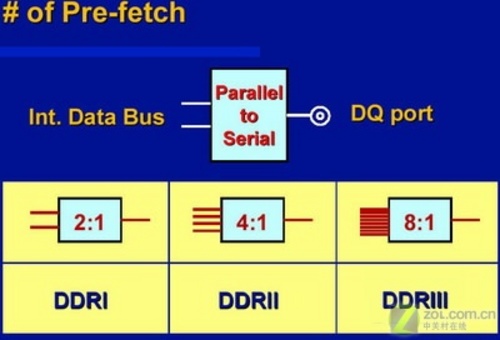

不同DDR类型引脚变化

DDR从一代进化到现在的DDR4,再到DDR5,其引脚的布局也在持续地演变。以DDR5为例,它在引脚的数量和功能上与DDR4存在差异。DDR5为了达到更高的数据传输速度,引入了若干新的引脚类型,以支持新增的功能。

在演变过程中,之前的设计理念有所调整。比如,随着工作频率的提升,DDR5中的时钟引脚变得尤为重要,其位置和防护措施比DDR4更为优化。此外,DDR5容量增加,导致地址引脚等关键引脚的布局更加紧密和合理。

你对DDR4和DDR5引脚布局在高速数据传输方面的差异是否有所了解?不妨在评论区留下你的见解或疑问,同时,也欢迎点赞并转发这篇文章。