一概述

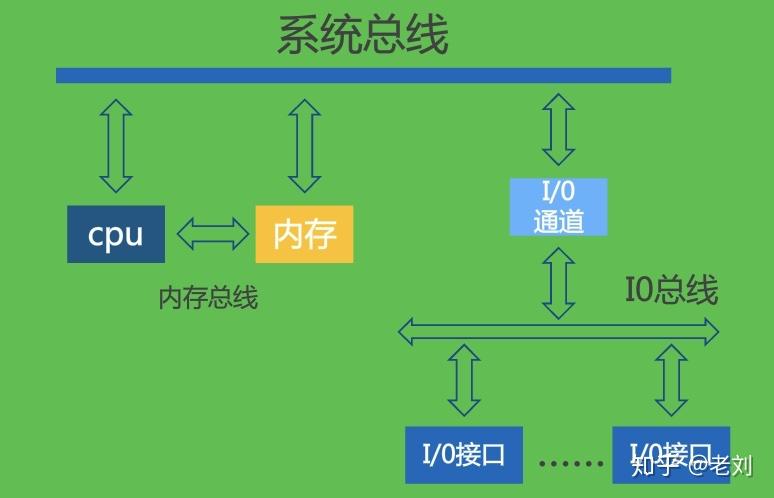

DDR时序对ARM系统性能影响极大。这关乎数据在内存与处理器间传输的时间安排。恰当的时序能确保数据准确且迅速传输,正如交通信号灯有序引导车流。若时序设置不当,可能引发数据传输错误或系统不稳定等问题。它包含诸如地址建立时间、读写数据保持时间等多个参数。

在ARM系统中,DDR时序的调整对整体性能至关重要。从系统设计的角度来看,我们必须针对不同DDR内存芯片的特性,精确地设定时序。这不仅是构建稳定高性能ARM系统的关键,也是不可或缺的一环。

二地址时序

地址的建立时间至关重要。在数据传输开始之前,必须先确定数据的准确地址。若地址建立时间不够充分,系统可能无法找到正确的存储位置。这好比你去图书馆找书,若不给管理员充足的时间查找索引,你自然无法拿到正确的书籍。此外,地址的保持时间也需适宜,否则,即使地址已失效,数据仍在传输中,也可能会出现错误。

ARM系统中的DDR地址时序,在不同应用场景下,还需进行优化调整。无论是针对大数据量的存储读取,还是小数据量的快速交互,地址时序都需与具体需求相匹配。

三数据读写时序

读取数据时,数据是从DDR内存中提取出来的。在这个过程中,数据的读取顺序必须与系统的时序逻辑相匹配。如果读取的数据提前或延迟到达ARM处理器,可能会导致数据错误。这就好比火车必须按照时刻表准时到达站台。同样,在写入数据时也是如此,对DDR进行写入操作时,数据保留的时间要适宜,否则写入的数据可能会出现不准确的情况。

且在ARM平台开发期间,开发者需针对不同DDR型号,反复调整数据读写时序,以适应ARM硬件的逻辑。这一过程耗时耗力,却是实现开发目标的关键环节。

四时钟时序

时钟信号如同DDR时序的指挥棒。只有合适的时钟频率,DDR才能正常运作。频率过高,DDR时序会陷入混乱,犹如乐队节奏过快造成的一片嘈杂。频率过低,DDR的高速性能也无法得到充分发挥。在ARM系统中,时钟时序的设置必须与整个系统的时钟源保持一致。

时钟的占空比是个不可忽视的考量。一旦占空比失衡,时钟的上升沿和下降沿的操作便会受影响。这样的问题会导致信号同步出现困难,进而影响数据在DDR中的传输效果。

五预充电和刷新时序

DDR使用一段时间后,必须进行预充电操作。这一步骤是为了确保后续数据传输的顺利进行。若预充电的时序安排不当,便可能导致数据无法准确写入或读取,就像汽车没加油却想继续行驶一样,是不可行的。

保持DDR数据完整的关键在于定期刷新操作。若刷新时机不当,数据完整性将受到威胁,甚至可能发生数据丢失。在ARM系统设计中,必须综合考虑DDR的存储容量以及应用环境等多种因素,从而合理设置预充电和刷新的时序。

六时序优化策略

首先,在硬件方面,我们可以通过优化PCB布局来提升时序性能。比如,缩短信号传输线路的长度,这样可以降低信号延迟,使时序更为精确。这好比给运动员安排了一个更近的起跑线。再者,在软件层面,我们可以运用一些时序调整算法。这些算法能够弥补硬件上难以避免的时序误差。

在实际的项目操作中,ARMDDR时序优化的高效方法正变得越来越受关注。大家在进行日常开发时,是否遇到过特别棘手的ARMDDR时序问题?若您觉得这篇文章对您有所帮助,不妨点赞并分享。