FPGA,即现场可编程门阵列,挂载DDR,也就是双倍数据速率同步动态随机存储器,这在电子工程领域是一项既复杂又至关重要的操作。对于众多从事相关开发工作的人员来说,掌握这项技术是必不可少的,它能够显著增强硬件系统的数据处理能力。

连接方式

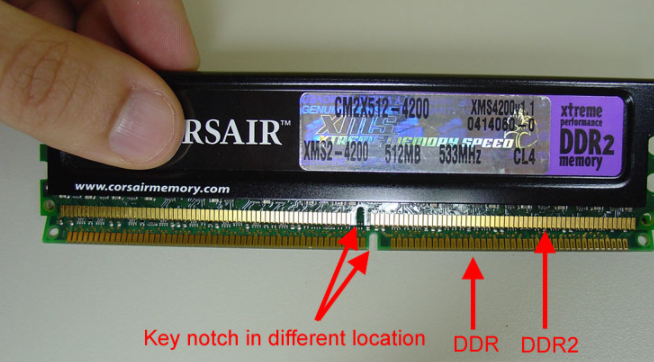

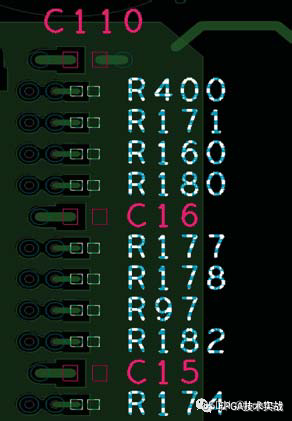

在FPGA与DDR的连接技术中,连接方式至关重要。硬件层面,每个DDR引脚都必须精确地连接到FPGA的相应引脚,误差丝毫不能容忍。例如,DDR的地址线、数据线与控制线等必须一一对应,否则将引发严重问题,甚至可能导致整个系统无法正常运作。在逻辑层面,FPGA内部需通过逻辑代码准确映射连接关系,并充分考虑DDR的工作模式等多种因素。仅仅物理线路的连接是远远不够的,逻辑上的精确同样必不可少,只有这样,数据才能在FPGA与DDR之间高效传输。

硬件电路板的布局对连接方式有显著影响。合理的布局有助于降低信号干扰,而布局不当则可能引发电磁兼容的严重问题。电路板布线若不合理,数据传输错误或信号衰减的风险增加,进而使得DDR与FPGA难以正常协同工作。

数据读写

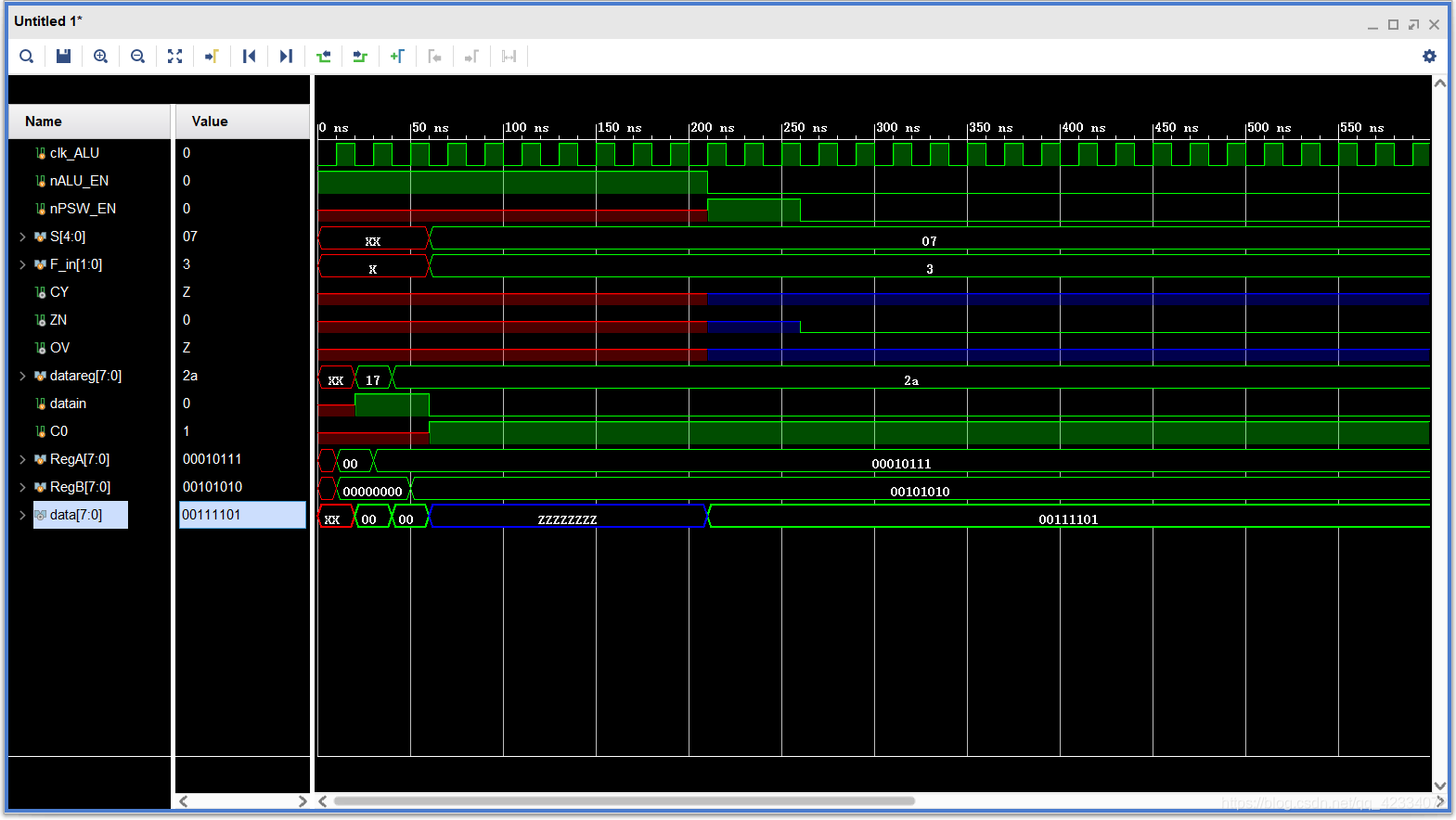

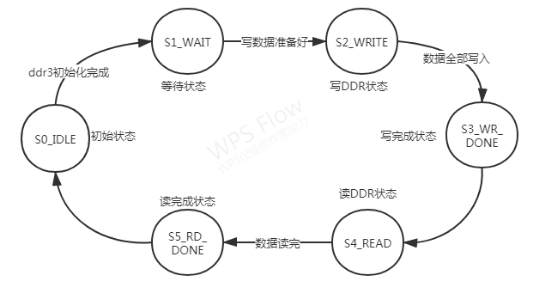

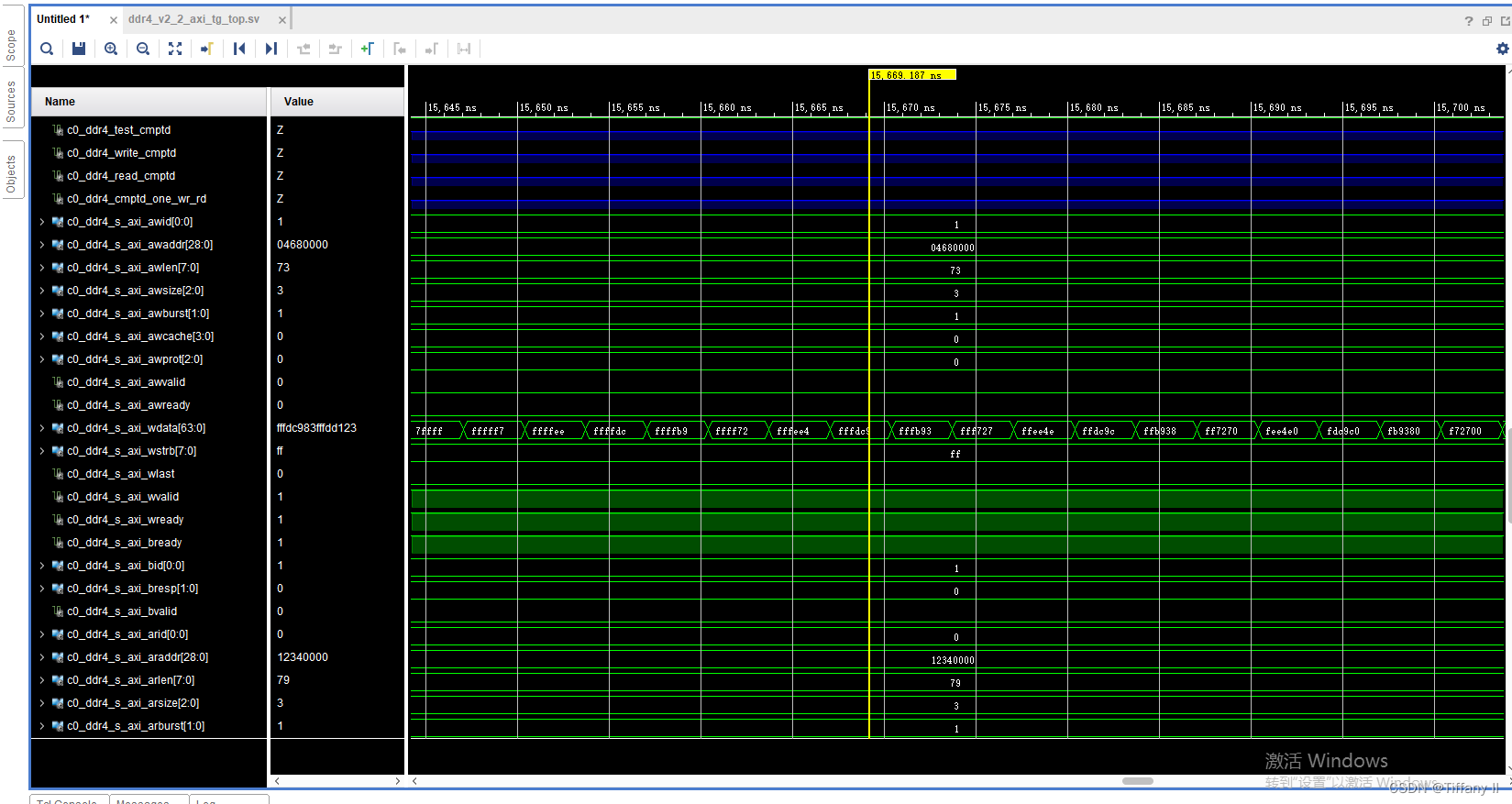

先弄明白读取数据的过程。在使用FPGA从DDR读取数据时,必须遵循一定的协议来执行操作。这个协议详细说明了数据读取的时序、地址请求的顺序以及响应方式等一系列规定。比如DDR3协议,就明确了列地址和行地址的发送顺序。若不遵循这些规定,数据就无法正确读取,甚至会出现读取错误。

写入数据时,需考虑的因素颇为繁杂。不仅要遵循写入的顺序,还得留意数据长度的合规性。在大规模数据传输的特定场景中,数据长度有时会超出DDR存储空间的原设限制。若不进行恰当的分割和写入控制,可能会引发数据丢失或DDR故障。

初始化设置

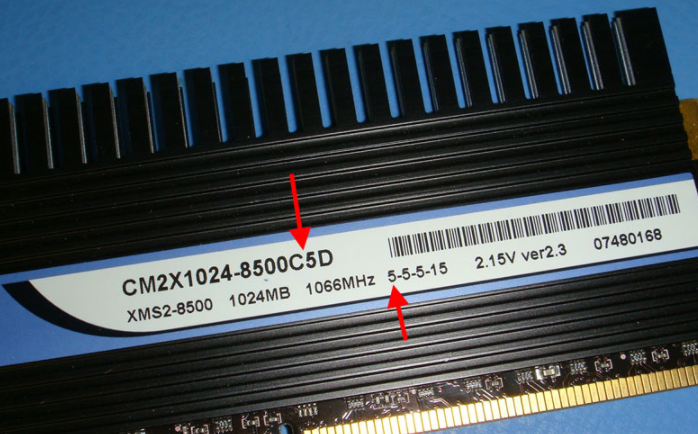

初始化DDR至关重要。DDR内部包含众多寄存器,必须准确配置。以DDR芯片为例,时钟频率相关的寄存器需设定恰当数值。若时钟频率设置过高,DDR可能无法稳定运行,引发数据错误;若设置过低,DDR的数据传输能力将无法充分发挥。

在初始化阶段,必须挑选DDR的工作模式。不同的模式适用于不同的应用环境。比如,在那些对能耗要求不高的系统里,挑选适合的低功耗模式来初始化DDR,不仅能有效减少电力消耗,同时也能满足系统对数据处理的各项需求。

带宽优化

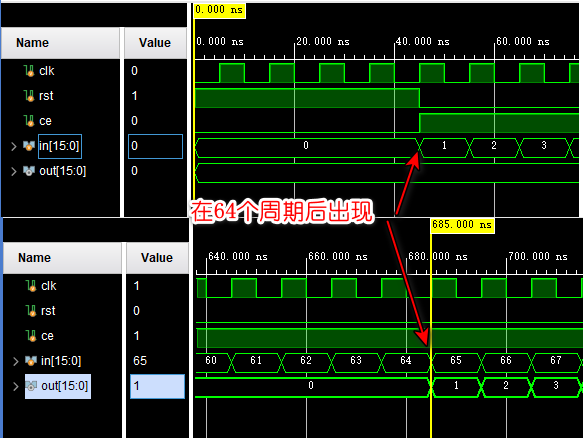

为了充分发挥DDR的高性能,带宽的优化显得尤为重要。在FPGA这一端,我们可以通过并行操作的方式提升带宽。例如,可以同时发起多个数据的读写请求,这样做能有效提升数据传输的效率。然而,在实施这一策略时,必须注意数据的同步问题,以免造成数据混乱。

DDR本身合理配置预读取等参数,可以增强数据传输带宽。预读取功能能在恰当的时刻预先准备后续数据,使得FPGA在需要读取时能迅速获取信息。然而,若预读取参数设置不当,可能会导致数据准备过多或过少,进而影响实际应用效果。

错误处理

FPGA搭载DDR的系统运行时,很可能会遭遇错误。其中,数据传输错误尤为常见。这错误可能源于线路干扰、DDR芯片自身问题或FPGA逻辑错误。一旦发现数据传输错误,需采取恢复措施。比如,可以重新发送数据或执行纠错操作。

另一个常见错误是地址映射出错。这样的错误可能造成数据被写入错误地址,或从错误地址读取数据。为了防止此类问题,系统设计及测试阶段必须进行全面地址映射的审查。同时,在硬件和软件层面都要采取相应措施,以预防此类错误的发生。

应用实例

图像视频处理领域应用广泛。比如在高清视频实时处理时,必须迅速读取并处理大量图像数据,处理完毕后再将其存储。采用FPGA结合DDR技术,能提供充足的存储空间和快速的数据交换能力。DDR的大容量存储空间可用来存放视频帧和图片等数据,而FPGA则负责图像的算法处理,例如执行边缘检测和色彩调整等操作。

网络通信设备中,类似路由器这样的设备,因其需处理大量数据包,FPGA搭配DDR技术被广泛运用以缓存数据包。这种方式能迅速读取与处理数据,有效提升了网络通信的速度和稳定性。若缺乏这种硬件组合,网络数据包处理不及时,可能导致网络拥堵等问题。

各位,有个疑问想请教:在进行FPGA连接DDR的操作过程中,大家最常忽视的是哪个环节?期待大家在评论区留言分享。另外,若觉得这篇文章有价值,别忘了点赞和转发!