DDR(双倍数据速率)系统中,多组DQS扮演着至关重要的角色。DQS,即数据选通信号,它的存在使得数据传输既高效又稳定。在处理复杂的数据读写时,DQS犹如一位精准的指挥者,引领着数据的精确传输。

DQS的基本定义

DQS实际上是一种信号控制机制。DDR的数据传输速度非常快,但若没有精确的选通信号,数据传输就会出错。DQS能够精确地调控数据传输的时间窗口。在电路设计实践中,这就要求我们根据DDR的实际运行频率等因素,精确地设定DQS的各项参数。它就如同交通信号灯,有条不紊地引导数据车辆的行驶。一旦DQS出现故障,数据传输就会变得如同没有交通灯的路口一般,一片混乱。

DDR技术发展至今,多组DQS的引入显得尤为必要。DDR的容量和传输速度不断升级,单组DQS已无法满足日益复杂的数据传输需求。多组DQS在更高频率下能确保数据传输的准确性。以DDR从低世代向高世代演进为例,每一代的数据传输量都在增加,而多组DQS在精准控制数据传输方向上的作用愈发凸显。

多组DQS的布局

DQS的布局设计颇为讲究。首先,必须确保信号完整,避免不同组DQS之间相互干扰。在DDR内存条上,布线设计需确保每组DQS能独立有效运作。其次,还需考虑空间利用,力求合理布局,实现既紧凑又功能完善的设计。

在制造过程中,若DQS布局多组设置不当,便可能引发信号串扰等问题。这些问题会导致DDR运行不稳定。例如,某些低价内存条在DQS布局上可能存在简化或不合理之处,这会影响到内存条的整体性能和稳定性。相比之下,高品质产品则会特别重视这一布局的优化。

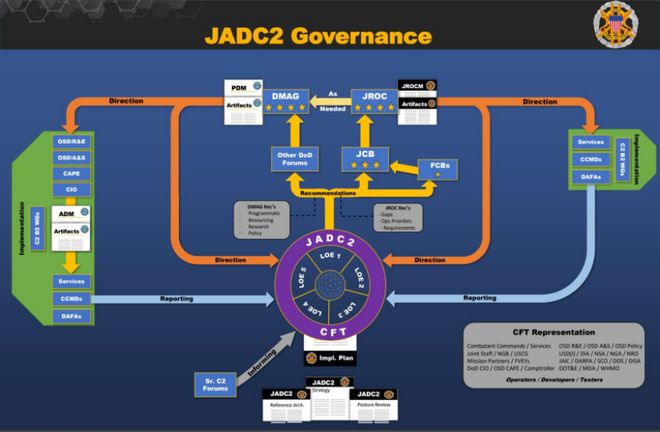

多组DQS的同步协调

多组DQS必须在运行中实现同步协调。这就像一支乐团中的不同乐器组,只有相互协作才能演奏出优美的旋律。在DDR芯片内部,设有特定的电路和逻辑,正是它们保证了多组DQS的同步。

在不同的应用环境中,比如服务器或普通PC机上,多组DQS同步的难度各不相同。服务器对数据传输的稳定性和准确性有更高的要求,因此在多组DQS同步的技术标准上更为严格。相较之下,普通PC机的需求较低。然而,一旦多组DQS同步出现故障,在高性能软件运行时,同样可能引发数据报错等问题。

多组DQS与内存带宽

DQS与内存带宽关系紧密。采用多组DQS能显著提升内存带宽。内存带宽指的是每秒钟可以传输的数据量,就好比一条公路的运输能力。在处理大量数据时,比如大型游戏加载或视频渲染,多组DQS能让数据更迅速地穿越内存通道。

若此处多组DQS发生故障或设计上存在缺陷,内存带宽将受到严重影响。打个比方,原本一条高速公路可以同时容纳双向八车道车辆行驶,相当于高带宽。然而,若负责管理车道运行的信号系统(即多组DQS)出现问题,那么这条路就只能实现单向两车道通行,带宽大幅降低。

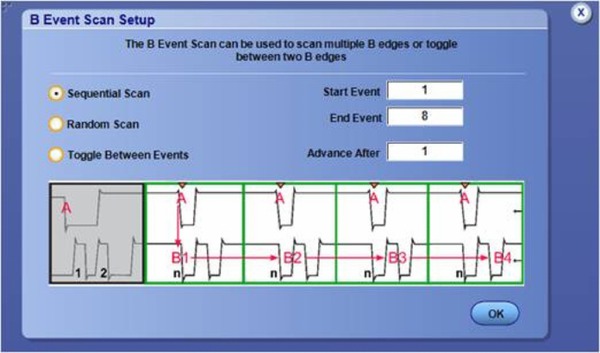

多组DQS的测试与调试

DDR的研发与生产环节中,对多组DQS的测试和调试显得尤为重要。实验室中,我们能够运用专门的测试设备,对多组DQS的各项参数进行检测。比如,信号的上升沿和下降沿是否满足既定标准。

调试时,技术人员需根据测试结果调整电路或参数。若发现DQS多组同步不一致,需探究原因,或许是线路元件故障,或许是软件算法控制不当。这过程类似医生诊断,需找准病根,再施以相应治疗。

多组DQS的未来发展

技术进步的脚步不曾停歇,多组DQS的性能优化已成为一种潮流。展望未来,或许我们将迎来更加智能化的多组DQS管理模式。DDR的速度持续攀升,多组DQS的发展也必须与时俱进。

观察行业发展,不难发现,随着人工智能与大数据应用的日益普及,对DDR的数据传输效率要求日益提高。在此背景下,多组DQS技术亟需不断创新以适应这一需求。关于多组DQS技术的未来走向,您有何高见?欢迎在评论区留言交流。同时,也期待您的点赞与分享,让更多人了解这一话题。