DDR,即双倍数据率同步动态随机存取存储器,它在计算机存储系统中占据着至关重要的位置。DDR前端代码,与之紧密相连,是不可或缺的关键部分。接下来,我将从几个方面对其进行详细阐述。

基本概念

DDR前端代码,首先要掌握几个基本概念。这些概念包括与DDR模块交互的接口逻辑等基础内容。以DDR3为例,代码需明确其读写操作的基本逻辑。有效控制DDR的数据读写,就像给复杂机器下达指令,步骤必须清晰。这要求对DDR内部架构有深入理解。若对DDR理解不足,编写代码就像在黑暗中摸索,毫无方向。只有掌握了基本概念,才能更好地构建前端代码。

编写DDR前端代码,会遇到不少与传统代码不一样的难题。必须考虑到DDR的高速度特性,这导致编写代码时必须进行特殊的时序处理。在编写过程中,务必保证代码能在高速环境下稳定且准确运行,否则任何微小的错误都可能导致严重的数据读取错误等问题。

常见错误

编写DDR前端代码时,开发者犯错并不稀奇。其中,时序设置不当是一个常见问题。例如,若读写命令的时序把握不准确,便可能造成数据传输的混乱。在工程实践中,若不小心将写命令的时序设置过早,DDR尚未准备好接收数据时便强行写入,可能会导致数据丢失或错误写入其他地址等严重后果。

需特别注意的还有地址映射的失误。DDR的地址空间有着明确的界定,一旦前端代码的地址映射逻辑出现误差,就可能将数据存放在错误的位置,或者访问到不应接触的数据。这就像把物品误放在了错误的抽屉里,找东西时自然会遇到麻烦。

优化策略

DDR前端代码的优化是提高性能的关键途径。我们首先应从代码结构入手。通过简化代码结构,可以减少逻辑的复杂性,例如,对那些繁杂的判断语句进行拆分或是优化组合。这就像是将一团乱麻整理得井井有条,从而使得代码的执行效率得到显著提升。

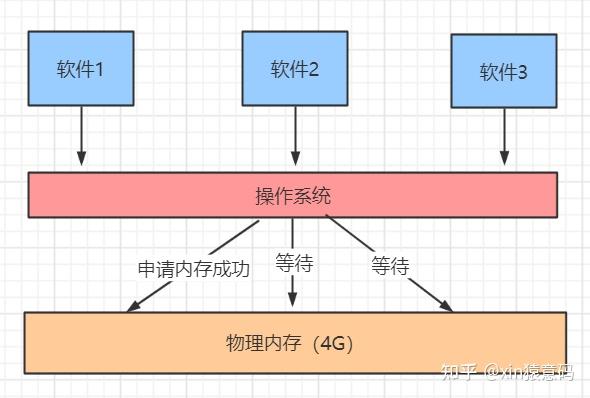

性能提升可以从缓存使用这一方面着手。恰当配置与运用缓存,可以减少对DDR的读写频率,就好比事先准备好所需工具,不必每次都去寻找。在处理大量数据读写时,这种方法能有效提升整体性能。

兼容性问题

DDR前端代码必须具备一定的兼容性。DDR各版本间特性与电气标准各异。比如,从DDR3升级至DDR4,前端代码若不作出相应调整,可能无法正常运行。代码需能适应DDR版本变化,或便于替换部分代码,以实现对新DDR特性的兼容。

此外,不同硬件平台对DDR前端代码的需求各不相同。比如,在ARM架构的平台和x86架构的平台中,可能需要调整前端代码的接口部分或初始化部分,这样才能满足不同架构对DDR操作的特殊要求。

调试方法

编写DDR前端代码时,调试环节至关重要。逻辑分析仪作为调试工具,其效果显著。它能捕捉DDR信号的时序,让我们直观地观察命令、数据和地址的传输顺序是否准确。若发现信号时序异常,可针对性地检查代码中相应的部分。

软件模拟是调试过程中的有效工具。在编写代码时,我们可以运用模拟工具来模拟DDR的运行状态,观察代码在模拟DDR环境中的表现。同时,我们还能轻松地修改代码,然后重新进行测试。这种方式有助于快速找出潜在的逻辑错误。

新技术对DDR前端代码的影响

技术不断进步,新技术亦对DDR前端代码产生了影响。比如,AI技术的崛起可能推动DDR前端代码走向智能化。在应对大数据量的AI应用场合,DDR前端代码或许需与AI算法协作,以实现数据调度的更高效率。

新出现的存储技术,比如3DXPoint,尽管与DDR存在差异,却对DDR的使用场景和应用产生了影响。因此,DDR的前端代码需要具备一定的预见性,在架构或接口上做出预留或调整,以应对未来的变化。

编写DDR前端代码时若遭遇兼容难题,应从何入手寻求解决方案?不妨在评论区留下你的见解。同时,也欢迎你为这篇文章点赞与转发。