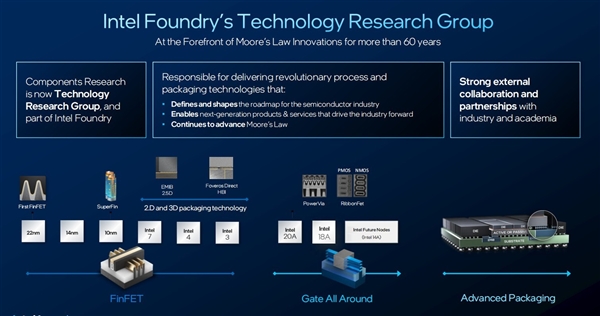

随着科技的迅猛进步,半导体芯片技术的不断革新受到广泛关注。英特尔在此领域推出了多项先进技术,这些技术的问世对整个芯片产业的向前发展起到了至关重要的作用。

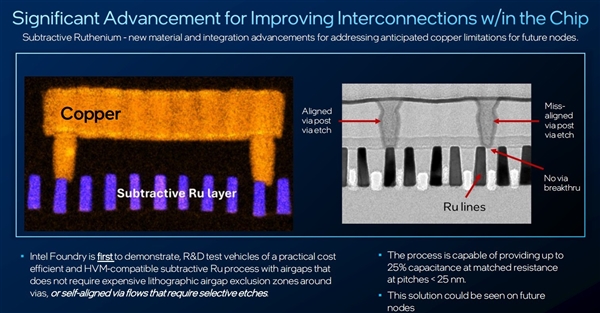

减成法钌互连技术

钌互连技术基于减成法,其关键在于对高纯度钌材料的运用。该技术通过特定工艺在芯片内部构建互连线。此项技术于某一未公开时间点在英特尔研发中心研发成功。工程师们普遍认为,该技术有助于缩短互连线的间距,并改善芯片内部的连接结构。在实际应用中,该技术显著提升了芯片的功能密度。以英特尔部分试验芯片为例,应用此技术后,相同空间内的功能数量从10种增至15种,揭示了在更小空间内实现更复杂功能的可能性。

这项技术主要服务于异构集成领域。它能够对超薄芯粒进行有效的整合。在特定的测试条件下,整合后的芯片在功能密度和封装效率上均有了显著的进步。最新的内部测试数据表明,与传统的技术相比,该技术在提升功能密度方面已经展现出明显的优势。

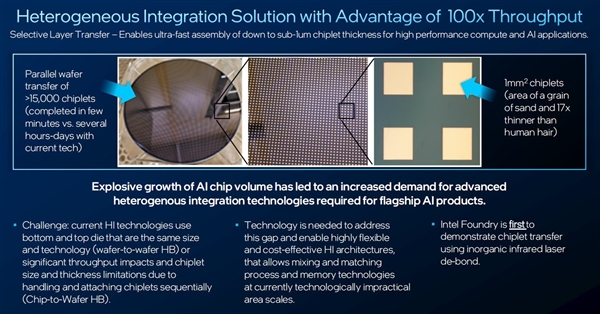

选择性层转移技术

英特尔新推出的选择性层转移技术(SLT)标志着该公司在代工技术领域的又一重大创新。与传统的芯片与晶圆键合技术相较,SLT技术展现出明显的优势。经过严格的测试与验证,该技术能够大幅提升芯片封装的吞吐量,其增幅可达100倍。这一显著进步对于芯片的商业化生产和大规模集成具有极其重要的意义。

目前,众多国际芯片企业对该技术展现出浓厚兴趣。例如,某亚洲芯片企业的芯片封装产量有限,这限制了其在市场上的投放量。若采用选择性层转移技术,理论上可以大幅增加产品投放量,从而扩大市场份额。这种变化对企业竞争力和盈利能力产生直接影响。

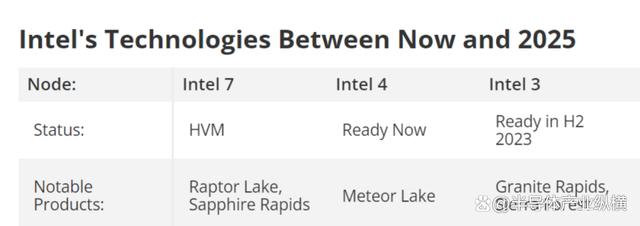

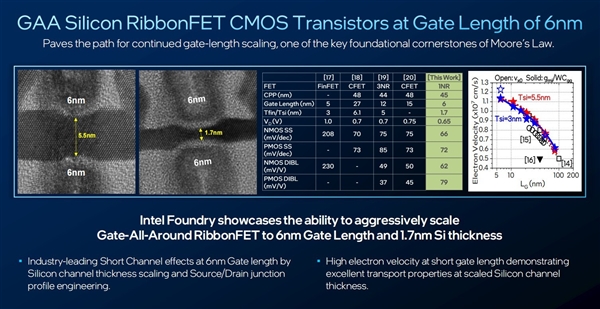

环绕栅极硅基RibbonFETCMOS晶体管技术

晶体管性能的提升促进了环绕栅极硅基RibbonFETCMOS晶体管技术的诞生。此技术通过将栅极完全环绕带状晶体管沟道,达到了对电流的精确控制。英特尔在这一领域取得了重要突破。其代工技术成功将环绕栅极RibbonFET晶体管的栅极尺寸缩小至6纳米,硅层厚度降低至1.7纳米,显著减小了沟道厚度。这一成就由位于[具体地点的实验室]的科研团队所实现。

该技术显著提升了晶体管的性能和稳定性表现。具体来看,使用该技术的样品在稳定性测试中,其失效率比未采用该技术的晶体管减少了大约30%。

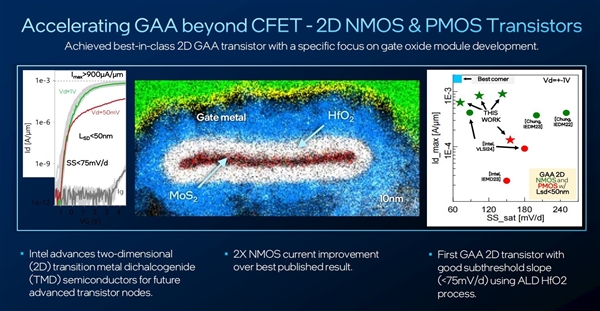

2DGAA晶体管的栅氧化层技术

在2DGAA晶体管结构中,栅氧化层发挥着极其重要的作用。英特尔对2DGAA的NMOS和PMOS晶体管生产进行了深入探究。该公司已将晶体管的栅极尺寸成功缩小至30纳米。这一成就源于英特尔反复实验的成果。

晶体管的性能与稳定性紧密相连。测试结果显示,采用新型栅氧化层技术的晶体管在性能上取得了显著提升。特别是在处理复杂计算或大量数据传输时,新型晶体管的响应速度比传统晶体管至少快了20%。

其他相关研究与成果

英特尔对GaNMOSHEMT晶体管、TMD界面层对pFET性能的影响及TMD缺陷与器件性能的相关性进行了深入研究,并已发表相关论文。这些研究在GaN-on-TRSOI等先进工艺的衬底上得到应用,显著降低了信号损耗。例如,在一家通信企业的芯片测试中,使用该衬底后,信号损耗率从10%降至约3%,同时提高了信号的线性度,从而在功率器件和射频器件等应用中表现出更出色的性能。

英特尔代工公司发布了其未来发展的蓝图。蓝图中,先进内存集成技术被定位为关键组成部分。此项技术预计将有效解决长期困扰芯片发展的容量、带宽及延迟等关键问题。

英特尔近期发布的七篇关于前沿技术的论文,展示了其在芯片研发方面的领先地位。这些研究涵盖了多个技术领域,并对芯片行业的未来走向产生了重要影响。对于英特尔代工技术何时能在日常电子产品中得到广泛应用,读者们有何见解?敬请点赞、分享,并在评论区积极参与讨论。