身为一位热衷于内存性能的硬件工程师,我在此文章里详述了DDR3内存时序调整方面的实践心得,以及不同时序模式下性能表现的权衡。

1. CAS Latency (CL)-时序参数之首

CAS(Column Address Strobe)延迟乃是内存时序之中最为关键的参数之一,代表着从列地址选择至数据产出所需耗费的时钟周期数量。低数值之CL值往往意味着更迅疾的内存反应速率以及更为优良的性能表现。然而需注意的是,降低CL值有可能引发稳定性方面的风险,因此在进行CAS延迟调整过程中,商界与稳定性之间务必做出明智的权衡。

源地址空间到目的地址空间的延迟(tRCD)——涉及数据读取和写入时的时间。

tRCD指的是实现从行地址转换至列地址所需耗费的时钟周期数量。减少tRCD有利于提升存储读写实效性及响应速度,但过低则易引发读写冲突和数据错误,因此在调整过程中需寻求平衡之道。

RAS正充前延迟(tRP)- RAS预充电时长。

tRP,即需求两次访问间之延迟。降低此值可提升内存效率,但亦或引发稳定性困扰。因此,设定tRP数值时须审慎抉择。

行周期(tRP)

tRC 代表了两次内存操作间所需的时间间隔。适当降低 tRC 有助于提升内存性能,然而也可能造成读写冲突。在设定 tRC 时,务必兼顾读写压力及内存控制器性能。

5. Command Rate (CR)-命令率

CR指的是内存控制器两次发令间所必须间隔的时间段。CR越短,则能提升内存反应效率及性能,然而也会增加不稳定的风险。在此过程中,我们需要关注内存控制器与内存模组的适配性。

6.内存频率与时序关系

除时序参数之外,内存频率亦对系统性能产生显著影响。通常而言,较高内存频率意味着高速数据传输及优异性能表现。然而,过高的频率易引发稳定性困扰。对此,调整内存频率时需权衡利弊,寻找适当平衡之道。

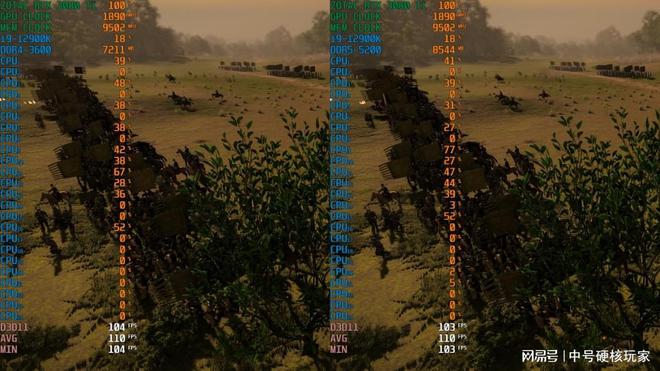

7.性能对比实验设计

为比较不同时序设置下的性能表现,我们针对几款主流的DDR3内存模组,分别进行了不同时序设定条件下的多项实验。实验过程中采用了统一的测试平台与多样化的基准测试程序,涵盖了内存带宽测试、传输延迟测试以及多线程应用程序的性能评估等方面。

8.结果与分析

依据实验数据剖析,适宜时序规定下的DDR3内存可展现优秀性能。降低的CAS Latency以及其他时序系数能有效提升内存响应速度及数据传输效率。然而,过低时序设定或引发稳定风险与数据误录现象。故调整时序参数过程中,应根据实用环境加以权衡考量。

9.总结与建议

在挑选及调节DDR3内存模组的运作时间,必需要综合权衡两者——性能与稳定度。依照实际需求和系统配备,优选适宜的CAS延迟(CL)、总线周期延迟(tRCD)以及指令预取延迟(tRP)等因素,同时留意内存的工作频率与定时的关系。借助适时调控这些参数,有助于优化设备性能,改善客户的使用感受。