本篇文章旨在通过分享作者致力于DDR FPGA开发的实战经验,以求让广大读者更深入地了解与掌握该技术。为达到此目的,文章将从理论基础逐步展开,详细阐述DDR FPGA 的基本工作机制、设计流程、常见问题难点及其对应解决方案,同时,将分享部分实践项目中所积累下来的宝贵经验与心得。

首先,我们需明晰ddr FPGA及其运作机理。DRD(双数据速率)为一高性能存储器接口科技手段;FPGA(现场可编程门阵列)则为一款灵活可编程电子元件。深刻洞悉上述概念将极大助力后续研发进程。

2.确定项目需求和目标

首先,项目需求及目标需得到清晰定义,以确保后续具体开发工作的顺利开展。此阶段应详尽分辨出对于存储容量,数据传输速率以及时序方面的严格要求。如此一来,方能使我们有针对性且高效地展开设计与优化过程。

3.设计ddr接口电路

在DDR FPGA开发环节,需精心设计接口电路联系FPGA与DRAM。此举包括时钟控制、数据及地址线设定等关键要素。在此过程中,须兼顾信号完整性、时序逻辑与能耗管理等各类影响因素,并实施的确切优化策略。

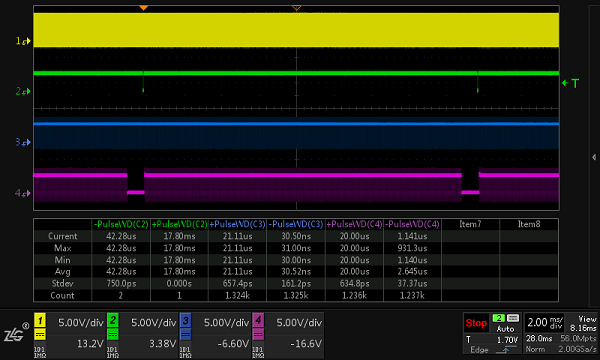

4.进行时序分析和优化

在DR FPGA研发中,时序分析与优化尤显关键,旨在保证信号在预定时间段内稳定传输且有效。通过科学规划及限制时序设置,可有效提升整体性能,规避信号冲突及时序违规等问题。

5.调试和验证

设计与布局完成后,亟需展开调试及验证工序。在此过程中,会对接口电路特性作深度检验,确保时序限制得到严格遵守甚至全系统功能亦将经历全面综合测试。凭借这些细致入微的调试及验证环节,问题将得以提前发现并得到妥善处理。

6.解决常见问题

在DDR FPGA研发进程中,时常会出现时序失准、信号传输劣化以及能耗过高等普遍问题。为有效应对这类挑战,我们可采纳一系列常规操作来处理,包括适度调整布局与电源控制策略等。

7.注意功耗管理

在DR FPGA开发进程中,重视功耗问题至关重要,特别是对于移动设备这类对能耗极为敏感的应用领域。经过合理的电源供应优化、适当范围内的时钟频率减小,以及采纳低耗能设计等方案,都能有效降低功耗,从而使得整个系统的性能与稳定性得以显著提升。

8.实际项目经验分享

除广泛涵盖之基础知识与技术外,我们将分享一系列在实战经历中所积累的宝贵经验,涉及选取恰当DDR FPGA芯片,以及系统级设计及调试等关键领域。期望这些实战案例能为您带来启示与实质的帮助。

9.持续学习和探索

在此,强调持久学习与考察的重要性乃是重中之重。DDR FPGA技术日新月异,我们需始终保持对新知识的探索热忱,以迅速掌握前沿科技动向及运用实例。唯有不断学习实践,方可在这一领域立于不败之地,为实际问题贡献更佳之解法。

通过上述九个方面的讨论,笔者期许准确把握和熟练运用DDR FPGA技术,从而在研发过程中降低失误风险,提高产品表现力与稳定性。作为多学科广泛采纳的关键技术,期望此文能为各位带来启示!