凭借在电子工程领域积累的丰富经验,我在此就DDR3阻抗问题进行深入探讨。期待能借助此文提升各位对DDR3阻抗的认知水平及实际操作能力。

1.什么是ddr3阻抗?

DDR3阻抗体现了其对信号流通的抑制能力,这在很大程度上决定了信息传输的质量与速度。在DDR3系统中,设定及调整阻抗参数可有效增进信号完整性与整体系统效能。

2.如何正确设置ddr3阻抗?

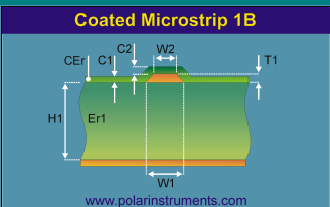

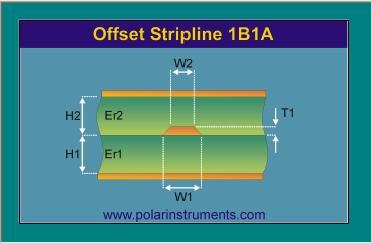

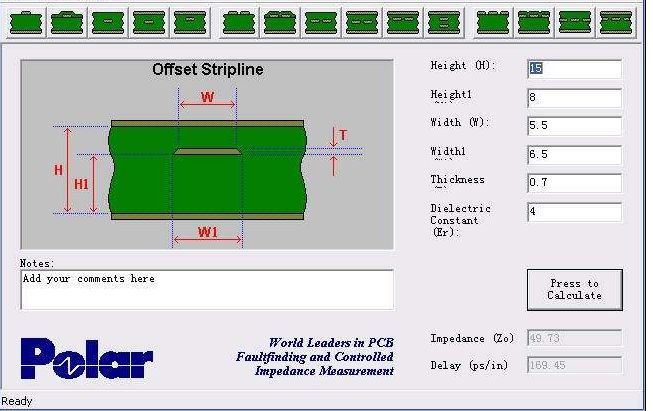

务必要熟知PCB板层次堆积的构造与属性特征,遵循规定的PCB设计标准以及参照厂商的数据手册,设定适宜之线宽、间隔及层间距离等参数。最后,借助专门仿真软件进行效果模拟并适时调整。

3. ddr3阻抗调整的注意事项

在调整ddr3阻抗时,需要注意以下几点:

-注意适度调节:频繁调节可能引发信号完整性问题或系统波动。

需关注信号传输方向,特定传输方可要求不同类型的阻抗匹配。

-捕捉气温变幻:温度之变更将影响阻抗数值,必须适时进行调节。

4.如何验证ddr3阻抗是否正确?

验证ddr3阻抗可以通过以下几种方式:

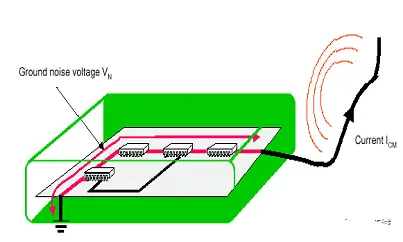

-使用高速示波器观测信号波形,检查是否存在反射和干扰。

-进行电磁兼容性测试,以确保系统在高频下能够正常工作。

-运行特定的测试程序,检查系统性能和稳定性。

5. ddr3阻抗调整的实践经验

在实践中,我总结了一些调整ddr3阻抗的经验:

-维持优质团队协作机制:与电路板设计专家及芯片制造商、测验工程师携手共斗,协同探索解决方案。

-多期迭代精进:首度设计成型后,实施数轮模拟与调整,至佳境而止。

-保持知识同步更新:紧密追踪科技进展,掌握最先进的DDR3阻抗调整策略与辅助工具。

6. ddr3阻抗调整的挑战和解决方案

在调节DDR3阻抗过程中,复杂线路布局以及信号质量稳定是我们需面对的主要挑战。要应对这类难题,必须深刻理解DDR3阻抗学问及相关理论,同时还要能够熟练应用各类工具和技术策略。

7. ddr3阻抗优化的效果

经适当实施DDR3阻抗调节与优化,可显著提升系统效能,降低数据传输出错率及时延,并在节能降耗以及降低辐射方面取得显著成果。

8. ddr3阻抗的未来发展趋势

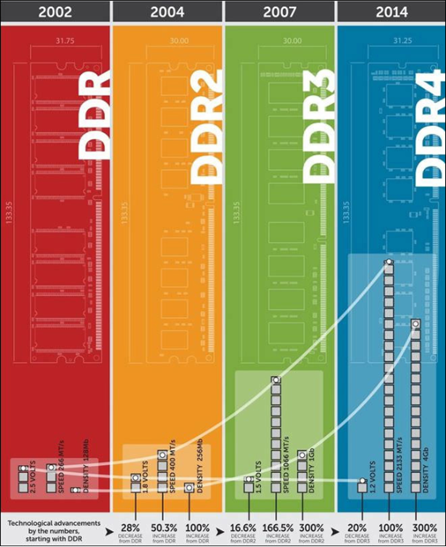

随着科技飞速发展,DDR3抵御能力调节方式亦在推陈出新。展望未来,我们有理由期盼更为尖端的模拟设备及计算方法,以及精度更高的抵抗匹配策略。

DDR3阻抗调控乃是电子工程中的要务,对于高速讯号传输具有决定性影响。恰当地调制与调节其参数,加之丰富的实践经验,能够极大地提升系统效能、减轻能耗负担,维护信号的完整及稳定。

本文旨在阐述个人所得经验与实践案例,以期助读者进一步理解并运用DDR3阻抗调整技术。未来,我将会持续深入钻研此议题,致力于为电子工程行业发展贡献更多力量。