身为一位专攻硬件设计领域的工程师,对于DDR3原理图,我具有深厚的理解。作为一款广泛运用的内存类型,它在现今的计算机体系中担当关键角色。借助探究DDR3原理图,了解其内在构造与工作模式,可为实际设计提供有力支持。

什么是DDR3原理图?

首先,我们需充分理解DDR3原理图所示,此乃描述DDR3内存模块电性连附件及讯号传输路径的蓝本。以此底图,清晰展现出DDR3内各功能模块间的具体连接关系及其电气属性参数。深入剖析DDR3原理图,有助于更全面地洞察其内部构造与运作机理。

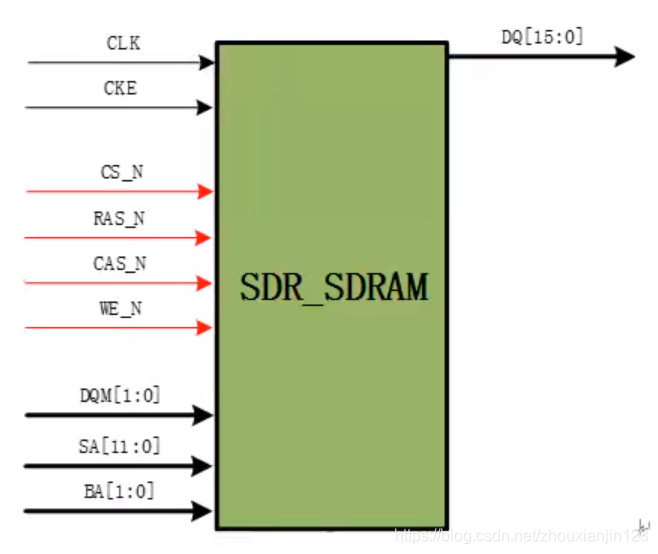

DDR3电路设计图常包含时钟、地址、数据及控制等关键信号的连接布局与走向细节。同时,也详尽标注了各元件的型号、引脚定义、电气特性等关键资料。掌握此信息,有助于明确各器件在整体系统中所担当的角色及其功能价值。

DDR3内部结构是怎样的?

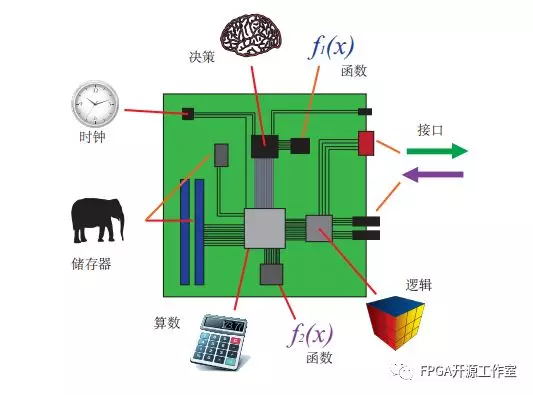

首先,我们来深入探讨一下DDR3内含的机构构造。这类内存模组通常包含了存储晶片、控制晶片以及时序控制器等等。其中,存储晶片作为模组的中心组件,它负责完成数据的存储和读/写过程。控制晶片的职责则在于维持各部分间的有效通讯及数据传输,时序控制器则保证了整个系统中各类信号通道能够按照指定的时间顺序进行信息传输。

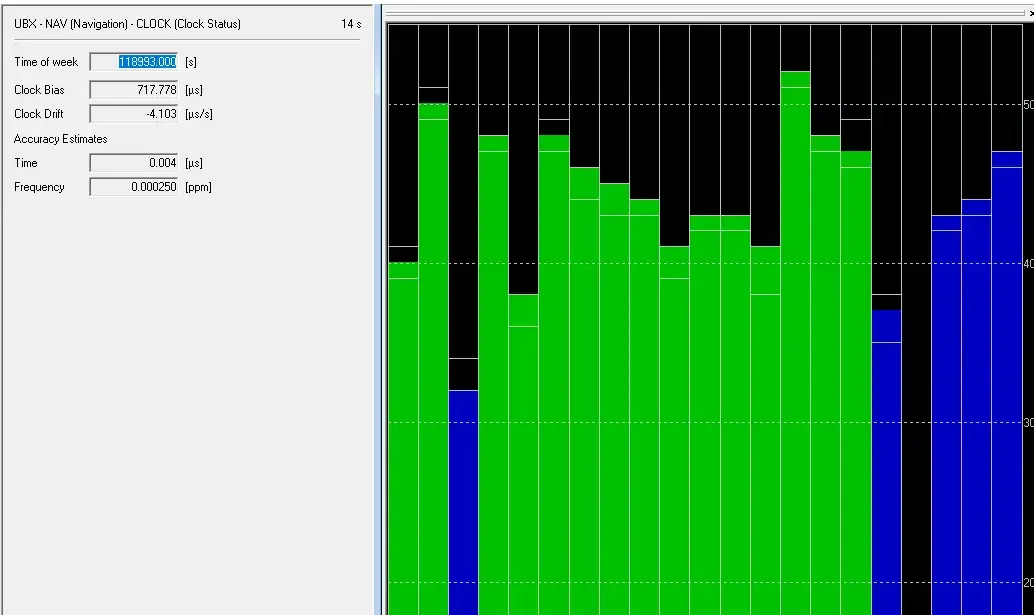

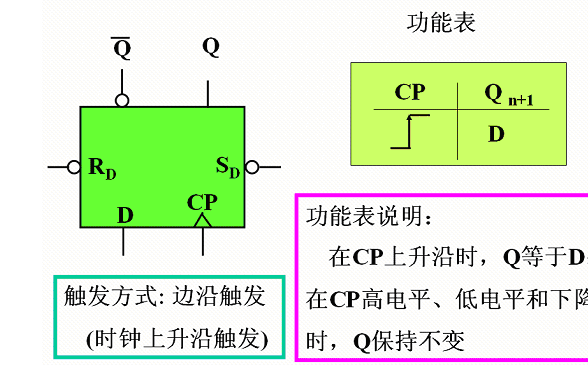

在DDR3的构造中,时钟信号发挥着决定性作用,由时钟发生器生成后传至各储存与掌控芯片,协调其操作次序准确无误;同时,地址与数据导线则负责传递存取信息,保障了读写过程顺畅运行。

DDR3原理图中的关键元件有哪些?

DDR3电路设计中,诸多重要元器件对整体运作起着至高无上的影响。首要提及的为存储器芯片,其具备解析并存储海量数据的能力;其次为控制器,肩负着高速处理数据流与实现处理器间互联交流的重任;再者便是时钟源,以稳定的时钟信号来确保各组件协同运作;以及数据缓冲器,助力提升数据传输速率。

此外,DDR3原理图中亦包含各类关键元件,如电源管理模块、阻抗匹配Email网路、以及终端电阻等。其中,电源管理模块致力于保障各元件的稳压供电环境;阻抗匹配Email则协调诸线路间阻抗差异,以提升信号传输性能;终端电阻用以消除信号线上的反射波,进而增进信号完整性。

如何设计一份完整且有效的DDR3原理图?

设计全面完善且高效的DDR3电路图需综合考量多个关键要素。首先要依据具体需求筛选合适的元件,包括确认内存容量与数据传输速度等重要参数;其次在布局环节,应明确元件间连结方法,确保无干扰及串扰现象;同时,布线阶段亦须关注信号完整性与能耗问题,根据实际情况灵活调整。

设计DDR3原理图应遵循相关标准与规定,保障设计符合业界标准,具备优良的可靠性与稳定性。仿真验证亦不可或缺,以证实体贴合性能需求并保持稳定可靠。

如何分析DDR3原理图中存在的问题?

针对正式场合的使用需求,我们可能会遭遇诸如读写操作出现错误、时钟频率频繁波动或存储量无法识别等疑难杂症。然而,透过深入剖析DDR3的电路构造,找出故障缘由并迅速制定相应修复措施是完全可行的。

对DDR3原理图的问题排查需以多元视角入手,包括核实每组件连接情况及电源有无异常;核查信息线路是否遭受干扰或串音影响;审视时钟信号是否保持稳定性等多个环节。依此类推,逐层剖析问题之症结,从而制定相应修复策略。

如何优化DDR3原理图设计?

为提升系统性能及降低能耗,在设计流程中应运用若干优化措施,如选用具备高速且低功耗特点的存储元件,精心调整布局与布线方案以降低信号干扰,以及优化电源管理器件以提升能效等手段。

此外,可采取差分对称技术以增强抗干扰性能,或增设终端电阻以解决反射波问题,甚至通过添加阻抗匹配网络来维护数据信号的完整性。实践证明,实施上述优化措施能显著提升DDR3系统性能和降低能耗。