身为电子工程领域的专业工程师,本人对DDR3原理图有深刻理解。这是一种通用的动态随机存取存储器(DRAM),其原理图囊括了诸多信号传输、时序控制及电源分配等关键元素。本文旨在详尽解说DDR3原理图的各个层面,涵盖其结构构造、运作机制、时序图表以及电气性质等方面,望能为广大读者提供详细且明晰的观察视角。

DDR3原理概述

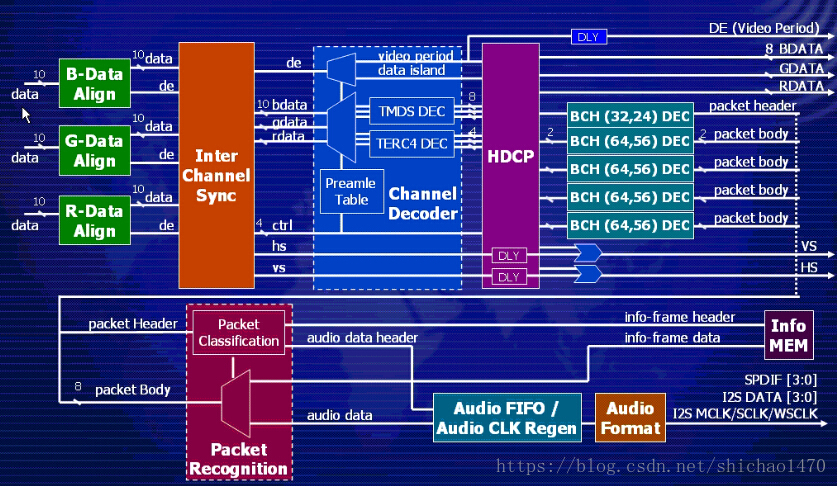

首先,让我们了解一下DDR3内部的架构特点。DDR3由存储模块、地址码及子系统、数据传输通道和控制器等多重组件组成。其中,存储模块用于存储信息,地址码及子系统用于定位目的地的位置,数据传输通路负责信息交互,而控制器则是信息读取与写入的决定性环节。各组成配件精诚协作,构建出DDR3丰富且精密的架构体系。

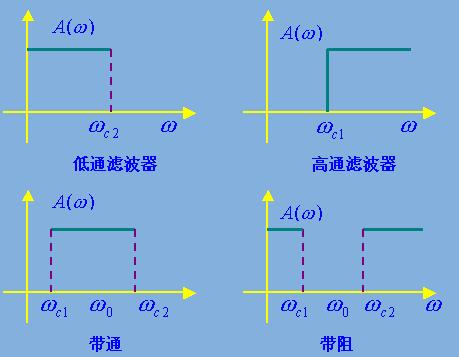

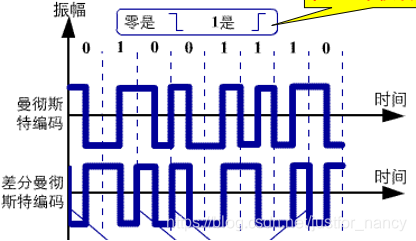

DDR3的双倍数据传输率,为其独特亮点。它采用差分信号传输技术且在上升与下降沿均进行数据传送,从而实现了双倍数据速率。此种架构能使DDR3在较短时间内传输大量数据,提升整体系统效能。

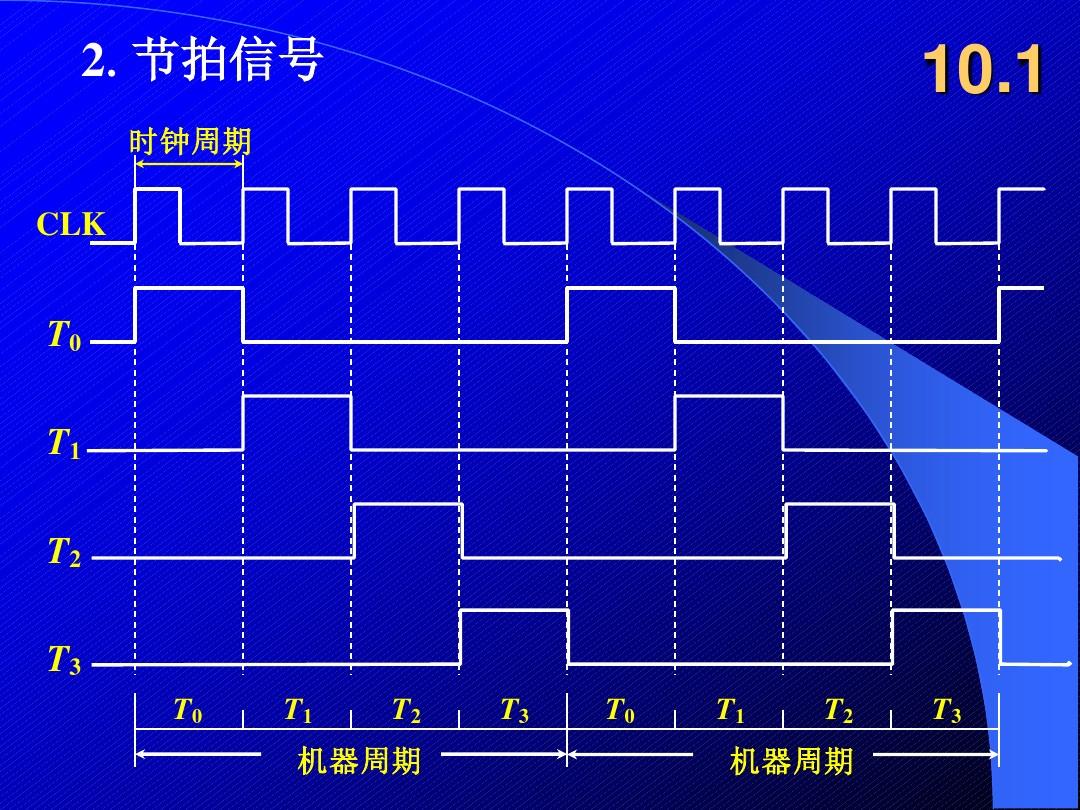

除此之外,DDR3功能中,时序控制模块的重要性不容忽视。该模块负责协调各信号间的时间顺序,使得数据得以按预期顺序读取与写入。时序控制模块必须严格遵守既定的时钟频率及时序规则,以保障系统稳定、高效地运作。

信号传输路径

现在,让我们深入探索DDR3原理图中的信号传输路径。在该设计中,信号经由内存控制器,通过主板上的轨迹抵达内存插槽,插槽与内存条之间的连接形成,并最终传至存储单元。全过程涉及众多信号线路,包括地址线、数据线和时钟信号等。

地址线明确指引了内存中数据所在,而数据线则承接实际传输之任。时钟信号发挥定向作用,确保各组件处于同频运转状态。此外,信号传输通道内尚有控制与校验信号等补充线路,以确保数据传输的精确度及稳固性。

在进行DDR3原理图设计过程中,合理规划信号传输路径尤为关键。优秀的布局设计能够缩减信号线长,降低干扰强度,从而提升系统抵御干扰和稳定运行的性能。同时,在高速信号传输的过程中,务必要关注到阻抗匹配与信号完整性的问题,进而保证信号质素达到行业标准的要求。

电源分配与供电管理

在DDR3原理图设计中,除了关注信号传输路线,必须重视电源分配与供电管理这部分关键内容。供电系统需保证各模块运行所需稳定可靠的电力供应,同时根据模块的功耗变化进行实时调整。

DDR3内存有两大主要供电体系—核心回路与I/O緩衝器供电。核心电力供应使內部逻辑电路正常运作,而I/O緩衝器供電則是为其外部功能模塊供电,如输入数据缓存、输出数据缓存等。妥善设置供电体系的架构及摆放位置能显著降低电源消耗以及热扩散,从而全面提升系统性能。

除此之外,电力供应管理应涵盖过压保护、欠压保护、过载保护等关键功能,以防备各种可能引发设备受损或产生故障的不良状况,从而保证系统的稳定长期运行。

时序图解析

在DDR3原理图解析中,时序图作为重要手段之一,严谨细致地展示了各项信号间的时间关联性。借助此技术,我们得以直观明了地理解信号间的运行顺序及时间差等重要参数。

基本的DDR3timer图表覆盖了初始设置、读取操作及写入操作等环节。初始阶段致力于各类精确定位与调控;不同於读取,其中包含地址请求、列选通以及数据的获取等更为复杂的具体环节;而在写入部分,其主要步骤包括地址请求、列选通运作并完成数据的妥善记录。

每个环节皆设有严谨的时间限定,这由内存控制器负责相关指令处理及反馈监控工作。精心筹划的时序图表有助于系统效能提升与读写速率的改善,对于故障排除乃至性能调试亦具有实质帮助。

电气特性分析

首先,让我们共同探讨DDR3原理图中所呈现出的电路技术特性。DDR3芯片内含诸多精密且深奥的电气特征,如电压负载能力、通道距离适配以及失调延迟调整等等。

总线负载强度即为连入总线设备的能耗占整体能耗的比例。在设计DDR3原理图阶段,需关注其是否超出特定范畴,从而避免因负载过重致通讯延误乃至失灵。

通道长度匹配直接关系到各条信号路径长度是否均衡。在高速通信情境下,若信道长度无法匹配合致,将会引发信号畸变或时延增大气象。故而,在DDR3原理设计环节,进行严格考量和统筹处理相关的通道长度匹配问题尤为重要。

偏移延迟校正旨在修正因双向总线的发送端与接收端间的时间差造成的问题。此项技术调整发送端的发送时间,以抵消接收端的接收时间偏移现象,进而保证双向通信的稳定性和可靠性。