身为一名资深数字设计工程师,我对DDR IP核拥有深厚的理解与掌握。作为现代芯片设计的重要组成部分,DDR IP核涵盖了内存控制器、时序调控及数据传输等多元领域。接下来,我将就DDR IP核的原理细节、设计流程、优化策略及实际运用进行深度剖析阐述,带着大家共同领略这项前沿技术的魅力。

什么是DDR IP核?

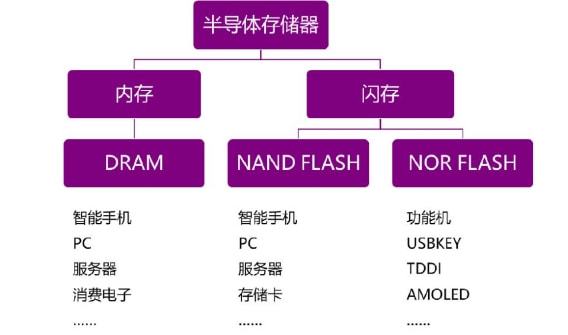

首先要明确的是DDR IP核的定义与属性。它所谓的"DDR"其实是Double Data Rate(双倍数据速率)的缩写,专指一种内存模组技术规格;而"IP核"则是Intellectual Property Core(知识产权核心)的简称,指称能被正确地集成至SoC(系统级芯片)中的特定模块。这样看来,DDR IP核实际上就是主要负责DDR内存控制及数据传输功能的知识产权核心。

在数字化设计领域,IP核以其独特的可重用性、功能性校验以及可靠性优异性,在打造复杂芯片架构的过程中,能发挥出显著的作用,大大缩短开发周期并降低研发成本。而DDR IP核作为这一重要组成部分,它专注于实现对DDR存储器相关的掌控与数据传输能力,更具有极高的适应性及个性化特点。

DDR IP核的工作原理是什么?

欲洞悉DDR IP核,需精熟其运作机制。DDR内存靠双倍数据速率传输技术,在单周期内传输双数位信息,整体提升了存储调取效能。因此,DDR IP核须遵从此双倍标准,并针对实际应用环境做精心设计。

DDR IP核在运行期间需承担诸多繁复任务,如时序把控、地址映射及数据缓存管理等。而此项工作的核心便是时序控制,即精准保证内存读写操作严格遵循预定时间序列并充分考虑信号传输延迟与时钟同步等影响因素。

DDR IP核需针对各类数据传输模式(如读入、写入及预取)提供稳定精确的支持,从而保障数据传输的可靠性。唯有全方位地设计并实现上述关键功能,方能使整个系统高速运作而无任何误差。

DDR IP核如何进行优化设计?

针对多样化的应用环境及性能诉求,DDR IP核心均可实施相应的优化策略。首要的便是时序优化,需在前期拟定阶段充分考虑信号传递延时、时钟分频比例与相位等相关要素,以便确保各项时序指标皆能达标,并达到理想的性能水平。

次之,针对如移动设备等对功耗高度敏感的场合,降低DDR IP核能耗至关重要。运用菲避峰、功率动态调控等创新技术,既可显著削减功耗,又能提高设备运行时长。

在此基础上,可对性能进行精进至优化设置。通过添加并行信道及提升频率响应,有望提高DDR IP核的运作效能,进一步提升其处理大量数据以及人工智能等相关应用的能力。

DDR IP核在实际应用中有哪些案例?

接下来让我们审视一下DDR IP核在实际运用中的几个核心案例。在移动电子设备,诸如智能手机和平板电脑这类产品上,广泛采用DDR IP核技术,进而达到高速内存读取以及顺畅的用户操作体验。

对于工业控制应用来说,诸如自动化设备与机器人系统这类设备通常依赖大容量且延时稳定的高速内存。通过采用高度优化过的DDR IP内核,便可显著提高系统运行效率并加速反应速率。

此外,DDR IP核亦广泛运用于云计算和数据中心等大规模计算环境中,协助管理大量的数据读取与写入过程,以确保系统稳健运行。

总的来看,DDR IP核作为现代芯片设计中至关重要的一环,其应用已覆盖广泛领域,且随着科技的持续发展将发挥更关键的角色。