身为一位资深的电子工程专家,我对于双数据率(DDR)硬件设计中的高速存储器接口技术——即DDR阻抗控制,有着独特且深刻的理解与经验。在这篇文章里,我将会全面剖析什么是DDR阻抗、阻抗控制的必要性、具体控制原理以及实现方法、最可能出现的问题及其解决策略等多方面内核话题,旨在增进广大读者对DDR阻抗控制技术的深度认知和实际操作运用能力。

什么是DDR阻抗?

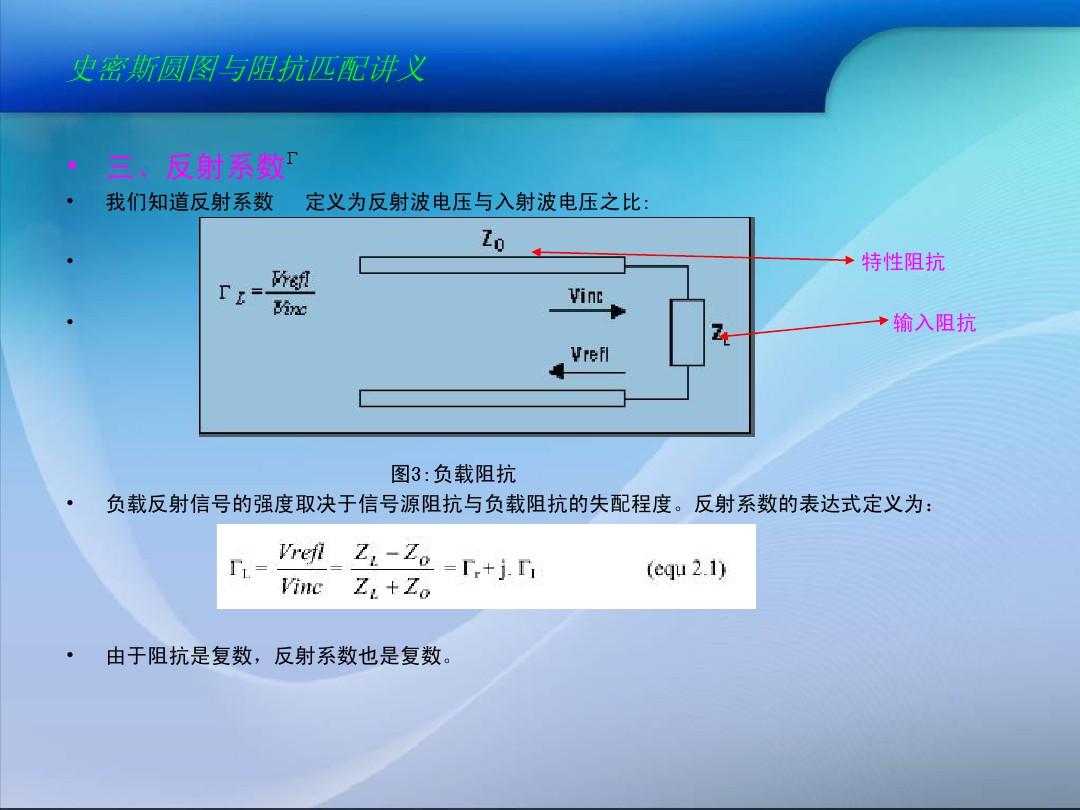

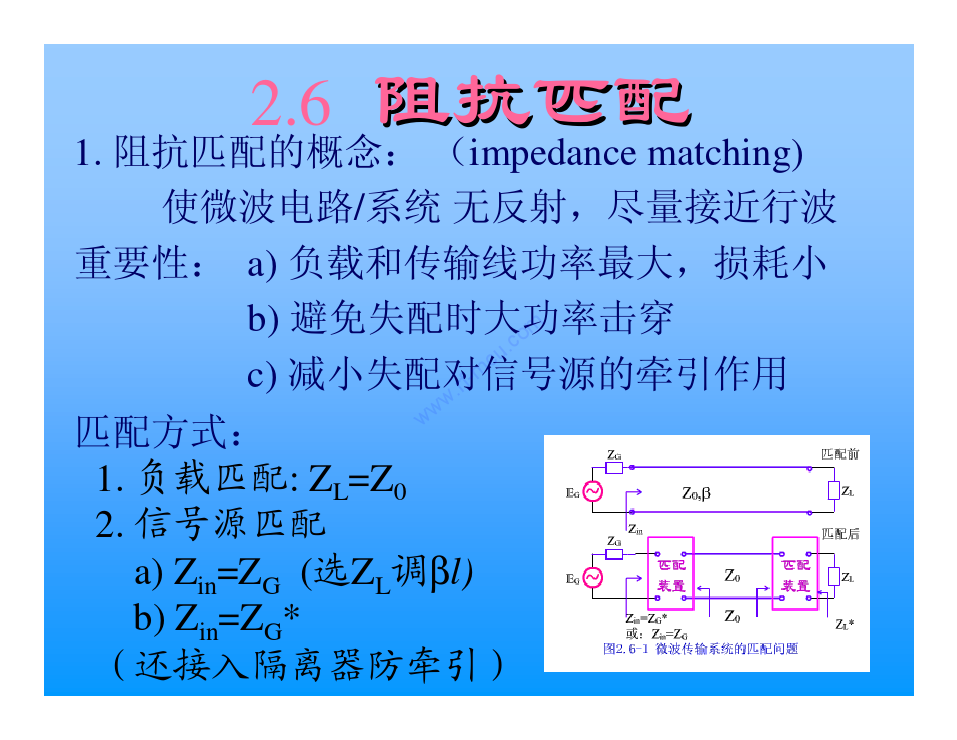

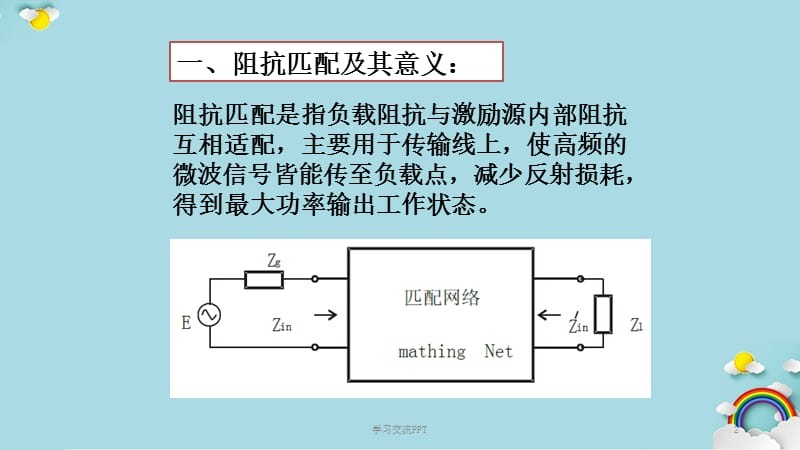

先明确,何为DDR阻抗。即DDR接口中信号线阻抗匹配至关重要,旨在保障无反射与干扰的信号传输,以提升系统稳定性及可靠性。直白说,阻抗即是电路对交流电源等效电阻,直接决定信号线波形质量及其传输速度。

在DDR接口中,严格设置差分信号线与单端信号线的特有阻抗值是非常必要的。前者倾向于选择50欧姆,后者则接近于75欧姆。通过精心规划并调整PCB板层间距、引脚布置及匹配电路等参数,我们能成功地调整DDR接口中各信号线的阻抗值,从而满足高速数据传输的严苛要求。

为何需要进行阻抗控制?

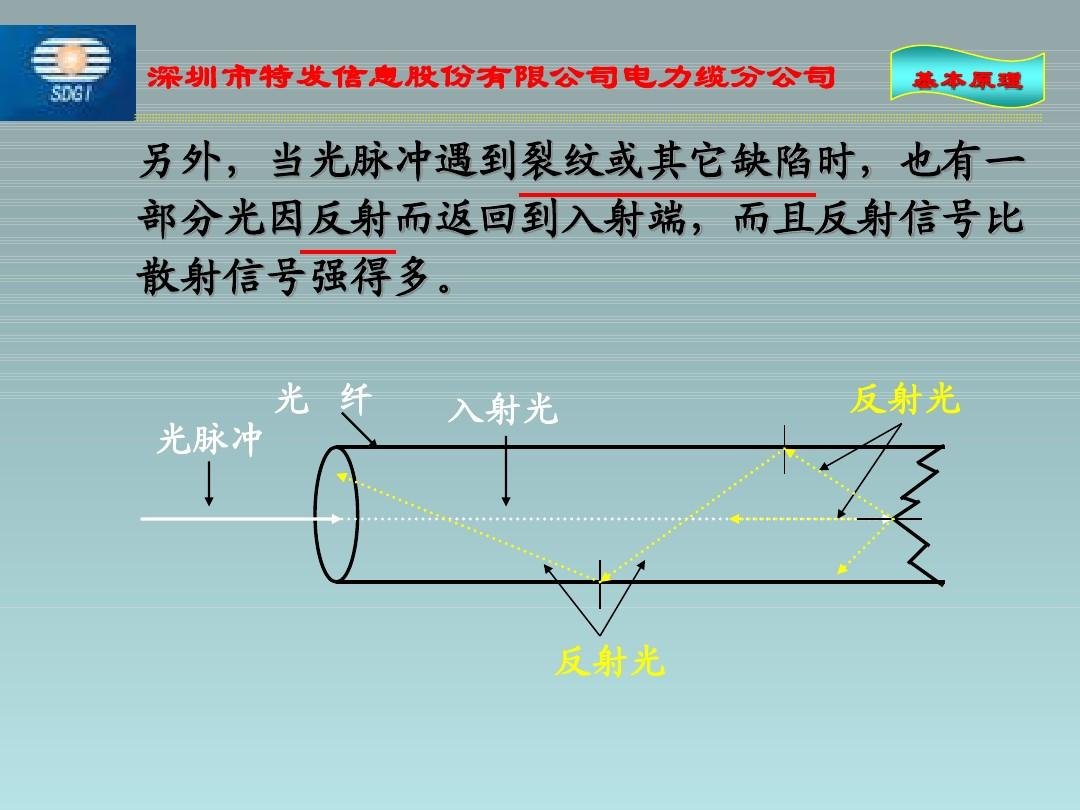

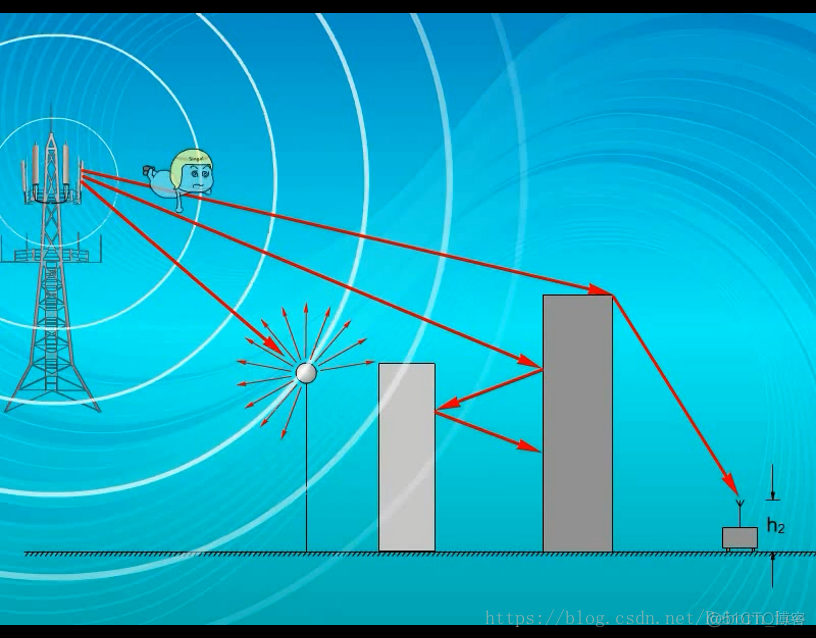

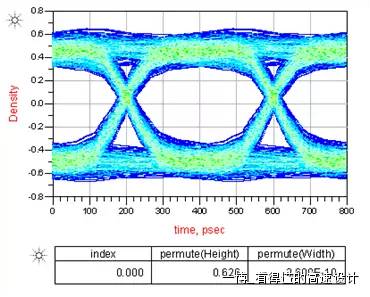

综观之下,为何需实施DDR阻抗调控?在纷繁复杂的高速传输环境下,若信号线阻抗未能完美协调,便可能引发信号反射及串扰等诸多问题,严重威胁到系统的稳定性与可靠性。此外,鉴于高速数据以及严苛的时序要求,DDR接口对于信号完整性的需求同样重要。

通过精确调控信号线阻抗值,既可减小反射与串扰所致之系统效能下降,亦有助于提升数据传输速度与稳定性。同时,精准匹配的阻抗也有利于降低能耗、增进系统电磁兼容性(EMC)表现。

DDR阻抗控制的原理

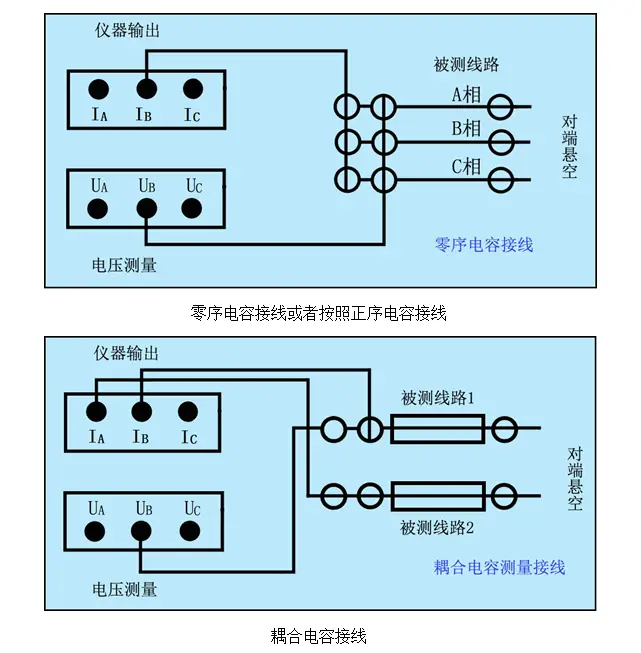

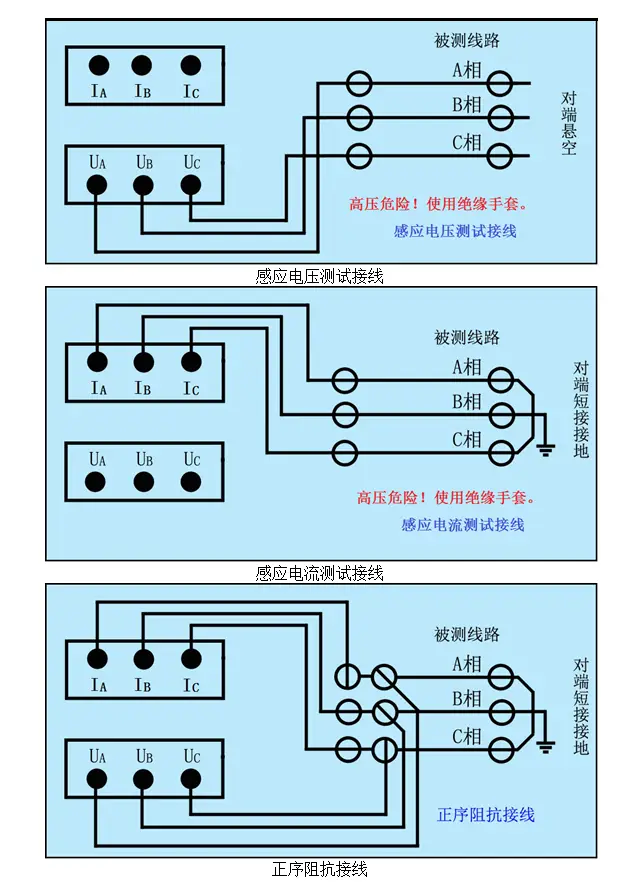

实行DDR阻抗控制的关键在于解决差分信号线上的匹配问题。在设计阶段应关注两根差分线及它们与地之间的净电阻状况。此外,由于存在互联电容和互联电感,因此它们在高频环境中对整体性能有重大影响。

在实际设计过程中,应全面考量差分对的长度、宽度和间隔等因素,然后通过仿真工具进行校验确认。为了尽量减少差分对之间及与其他信号的干扰,需在PCB板布局时选择合理的层叠方式以保障信号的完整传输。

实际上,DDR接口设计除了布线之外,也需充分考虑时序与功耗等诸多影响因素,根据具体情势作相应的调节和提升。

如何实施DDR阻抗匹配?

DDR阻抗匹配的实现需进行细致且复杂的整合分析。首先,需在设计初期着重关注此问题,进而根据实际需求选定适宜的PCB材料、层数及厚度等关键因素。在接下来的布局阶段中,需格外警惕布线路径与长度的合理性,以及为布置匹配网络提供充足的预留空间。

在实际操作中,我们需运用相关仿真工具进行验证,根据结果进行必要修正和调整。比如,可通过调节不同层级间的间距、增减引脚长度以达到期望的阻抗水平。同时,要挑选信得过的PCB板厂按设计需求进行精密制程制作。

实行上述步骤的DDR阻抗匹配可显著减少设计风险,提升系统稳定性,且能保证数据传输质量合乎规范标准。

常见问题及解决方法

在实践操作过程中,时常出现诸如:信号干扰、反射噪音等常见难题。为有效应对此类情况,建议采纳以下处理方案:

信号干扰控制:可通过增加地孔数量或扩大接地填充区,以缩短地回流通路。同时,加装隔音罩或增设屏蔽墙体还能有效隔绝干扰源。

减少反射噪声:可通过加装终端电阻或调控驱动输出电压的方式来降低反射波幅度,亦或是调节布局使反射波与主波形的到达时间同步。

总的来说,实际设计过程需着重考量多种因素且经严谨验证,以保证系统在各类工况下皆可稳定运作。