什么是DDR接口?

首先,需明晰DDR乃Double Data Rate之缩写,意为双倍数据传输率。它作为专用于内存条与主板间信息传递的接口规范,立足于提高数据传输率及效能。借助于利用上升沿与下降沿两个时钟周期传送数据这一方式,DDR接口实现了在特定时间内传送两倍数据总量,极大地提升了资料传输速度。

在实践运用上,各世代DDR标准(如DDR3、DDR4及LPDDR4)因其数据传输速度与规范特性的差异而有所区分。每种DDR标准均采用独特接口定义,且需严格遵嘱其规范指导,方能保障系统稳健运行。

DDR接口的时序要求有哪些?

对于DDR类型的接驳口而言,時序起到决定性作用。它涵盖了各类信号线间的传送时间和其间的关系。在研发过程中,必须精密调整时钟信号、地址信号、控制信号与数据信号间的时差,保证各类信号能以最佳时机抵达指定位置。

在实施印刷电路板布局时,务必考量因信号线长度引发的时间延迟问题,并需运用适当布线及长度调配策略以确保各信号无缝地抵达目标节点。唯有严格符合精确的时序需求,方能确保系统平稳顺畅地进行读写操作,避免数据误差或遗失现象发生。

DDR接口的信号电气特性有哪些?

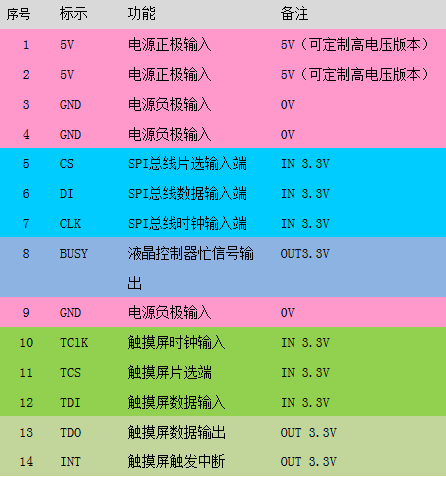

在满足时序需求之外,我们还需关注DDR接口一组至关重要的信号电学性质。这些性质涵盖如下方面:

传输速率:该指标反映了设备在单位时间内能处理的信息容量,DDR标准习惯用MT/s作为衡量单位。

电源电压:依据不同时期内的DDR标准,其供电电压亦有所差异,在设计过程中,需严格按照规范进行选用。

阻抗匹配:为避免反射及串扰,PCB设计需确保信号路径与两端阻抗匹配。

保持信号质量:涉及控制噪音与减弱串扰两方面,须在精准布设中运用科学方法确保信号的优质传输。

抖动(Jitter)管控:抖动现象即时钟或数据信息波动偏离乃至失真,需在设计阶段高度注意对其控制,保障数据传输的精确性

如何进行DDR接口调试与优化?

在实践项目中,对DDR接口进行有效的调试和优化至关重要,以确保系统稳定而高效地运作。以下为几种常见的调试及优化策略:

时序解析:运用专业仪表如示波器、逻辑分析仪等精细测量,以及利用仿真软件深度剖析时序。

信号完整性验证:运用 SI 仿真工具进行大量模拟,以评估和完善布局方案。

对供电稳定性的检测需要确定供电设备运转情况是否稳定,然后给出相应的改善方案和优化措施。

环境污染检查:深入解析外界因素对本装置可能产生的影响,采用必要的防范措施如屏蔽与滤波等予以排除。

固件/驱动的更新与升级:针对已知问题进行相应固件或驱动程序的及时更新,以提高设备运行效率和稳定性。

未来DDR接口发展方向是什么?

随着计算科技的持续进步,对大内存带宽与容量的需求也日益增长。预计未来DDR界面的发展趋势主要在于:

未来DDR内存将借助先进的半导体工艺及创新设计突破高频率限制,以满足带宽日益增大的需求。

高效节能:鉴于移动设备等对功耗较为敏感的产品,未来的DDR标准将持续优化能耗模式,并研制出更为省电的新型品种。

高密度的趋势:在大数据及人工智能应用日益扩展的环境下,内存将出现对高密度需求的增长,同时DDR接口亦将朝向更高容量的方向演变。

提升兼容性:为实现系统的完美融合,未来DDR接口有望更出色地适应各种通信协议,例如PCIe和USB等。

本文对DDR接口定义进行了详尽解读。面对当今信息海量与科技迅猛之势,DDR接口这一硬件领域核心要素实具有举足轻重的价值!