身为资深的电脑硬件工程师,我明白内存对于计算机性能的决定性作用。其中,DDR3内存以其普及度成为焦点。我们不能忽视的是,DDR3内存存在的走线问题对系统性能产生着深远影响,因此合理优化显得至关重要。此文旨在分享我在实践中的经验和发现,希望能让阅读者认识到这一关键点并理解如何提高计算机的运行效率。

一、初识DDR3

首先,让我们对DDR3内存做一简要介绍。作为双倍数据率内存技术的代表,与上一代DDR2相比,DDR3在速度及带宽上都实现了质的飞跃。然要完全释放其潜能,则必须重视合理的布线设计。

二、信号完整性与走线规划

在线缆设计过程中,信号完整性不容忽视。它可有效提升数据通信的精确度与稳定性。以下两点建议有助实现良好的信号完整性:

缩短信号通道:通过精简信号传输路径可降低传输时延,减小干扰与损耗影响。

预防信号交互:信号交互易引发数据传输的不稳定现象,故需在布线时尽可能杜绝此情况发生。

关注差分对布线:DDR3内存采用差分对传递信息,所以需密切关注其布局并保持其协调。

三、电源和地线规划

除信号完整性之外,电源与地线的合理性规划同样对DDR3布线至关重要,能够降低噪声干扰,提高内存模块稳定性能。实际操作过程中的相关建议如下所述:

隔离电源与接地:通过分隔处理电源与地线,可有效防止两者间相互影响。

采用平坦布线进行供电与接地规划:在电路板设计环节,运用均匀布设电源及接地线路能有效降低电磁干扰并增强内存模块的稳定性。

四、细节决定成败

在执行DDR3走线优化工作时,关键在于注重细节之处。在此,我列举了几个重要且值得注意的细节问题:

确保信号层级统一:稳定的信号层次设定能够消除信号传播中的反射与串扰现象。

引导走线角度:通过科学规划走线角度,既可减少信号的干扰,亦可降低信号损失。

精细引脚布局:精妙的引脚分布能够有效减少信号干涉与干扰,进而增强内存模块的稳定性。

五、实践与总结

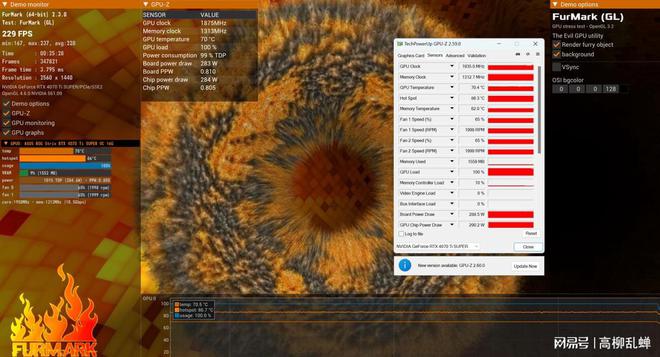

熟知实战经验后,我深感DDR3线路优化并非轻易达成。复杂的系统各具特色,需依具体情况独立定制优化方案。实践过程中须关注每项细节,勇于挖掘并汲取经验教训以取得最优效益。

六、未来展望

伴随着技术的日新月异更新换代,DDR3内存亟待新一代产品替代。然在此期间,DDR3摆设优化的重要性依旧不言而喻。客观地讲,我期望能借助这种方式,分享自己的实际操作经验,从而为广大读者提供科学有效的参考指引。

七、结语

对于DDR3走线优化,这是一项综合性极高的系统工程,需全面兼顾硬件设计、线路排布以及信号完整性。通过不懈探索与实践,我们有望进一步提升计算机性能,以提供更优质的用户体验。展望未来,DDR3走线优化必将在业内掀起新的热潮。

八、参考资料

DDR3 SDRAM 规格说明文档链接为:https://www.jedec.org/standards-documents/docs/jesd79-3f。