什么是DDR3端接电阻

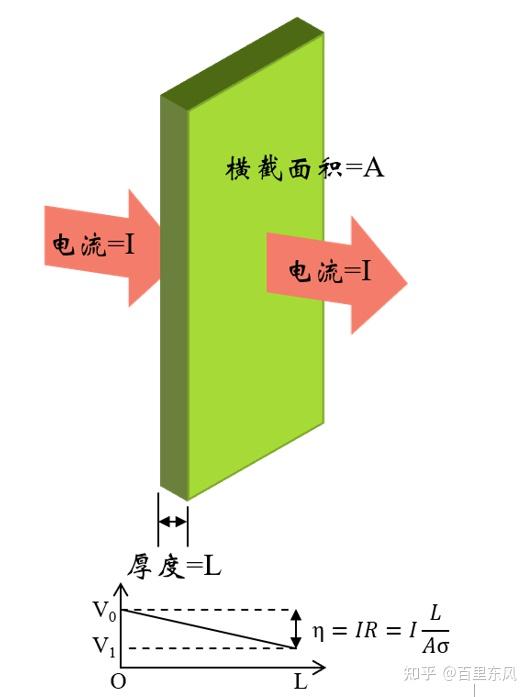

DDR3端接电阻是专为DDR3存储模组研发生产的关键器件,用以规范其数据接口的阻抗,有助有效降低信号反射及干扰。设计并合理选用端接电阻对提升信号质量、降低能源消耗以及提升系统稳定运行起到了举足轻重的作用。

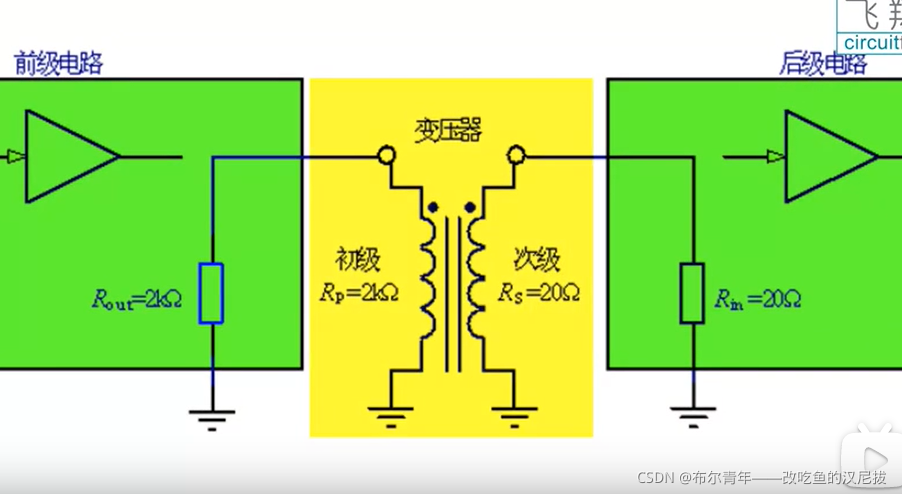

鉴于DDR3内存模块常见的64位总线架构以及高速数据传输速率,其信号传输的稳定度及可靠性显得至关重要。其中,端接电阻主要功能在于匹配传输线路阻抗以降低信号反射和串扰的影响,进而实现更为精准且高效的数据传输过程。

DDR3端接电阻的作用

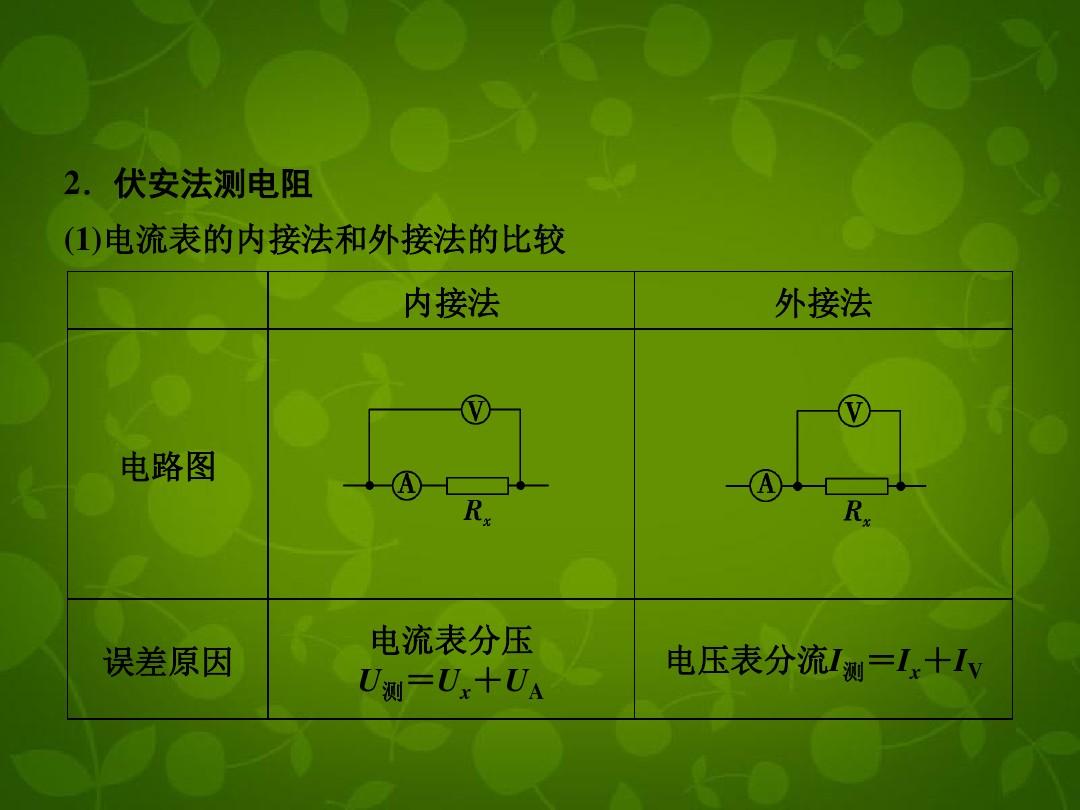

信号质量要求:由于DDR3内存芯片运行在高频状态下,故对于信号波形清晰度稳定性有较高需求,以防止出现数据错误或者遗漏现象。而端接电阻作用在于能精确调节信号波形上升与衰减过程,从而降低失真,提高整体信号品质。

阻抗适配:内存控制器、板载布局以及线路内层均会对信号线阻抗产生影响,故可根据实际需求调整端接电阻,使信号线阻抗更精确地达到适配标准。

降功耗:识别的正确配置端接电阻可有效地降低功耗损耗。信号波形受干扰或反向时,将产生额外功耗,可能引发系统稳定性问题;然而通过合理设定端接电阻,便能有效减轻功耗问题的影响。

抵抗串扰:鉴于64位总线体系的特性,各数据线间可能存在互相干扰。为此,实施适宜的端接电阻可显著降低并消除这一问题,从而提升系统稳定性。

如何选择合适的DDR3端接电阻

阻抗匹配:适当选用端接电阻数值极其关键,DDR3内存模块常采用50欧姆至75欧姆的端接电阻配套适传输线运用。

频响特性因素:务必根据所需内存工作频率挑选合适的端接电阻类型以保持信号完整性。择优时须重点考虑其频率响应能力优良与否。

封装规格:常见于DDR3内存模块的是0603或0402小型表面贴装式端接电阻。选适宜且便于焊接装配的产品,有益于生产及维修。

环境适配性:工作场所温度与湿度均会对端接电阻的性能造成影响。故而选购时须关注温、湿度敏感程度和相应的温度系数指标。

如何正确布局DDR3端接电阻

CPU附近的优先权:为降低数据传输延迟,在规划主板布局时,建议把DDR3内存插槽设置在离CPU较近处,且相应的端接电阻也要贴近CPU安置。

尊重对称原则:在64位总线架构内,保持数据线对等势在必行。各数据线间需等长并相应位置装设同值终端电阻。

调节走线长度:将数据线与端接电阻间距缩至最短,以减少信号传输延时及损耗。

抗干扰措施:相邻数据线路须有充足间距分隔并加装防护罩,防止信号串扰影响。此外,应据实际需求选取适当的终端电阻值。

如何正确焊接DDR3端接电阻

明确焊点位置:焊接操作之前,务必确定正确的端接电阻焊点位置,同时要查验是否存在错位和短路的现象。

精准控制焊接温度与时间:选择适宜温度的焊料进行焊接,严密把控焊温及焊接时间,以免因过热造成元器件损害。

精确摆位:务必正确安置端接电阻至PCB板,且须保证其方向定位无误。

审视焊点品质:施焊完毕,务必检验焊点质量,以免产生虚焊与短路等不良后果。

常见问题及解决方法

若错误选用端接电阻参数或型号,可能引发信号失真与稳定性问题;需采取措施更换正确的端接电阻。

若端接电阻焊点出现虚焊或短路,将直接影响其信号传输质量。故应立即对相关焊点进行重新检测及修整。

接头处的电阻与其他电子组件间产生问题,影响整体运行,应通过优化布局设计以减轻其影响。

未来发展趋势

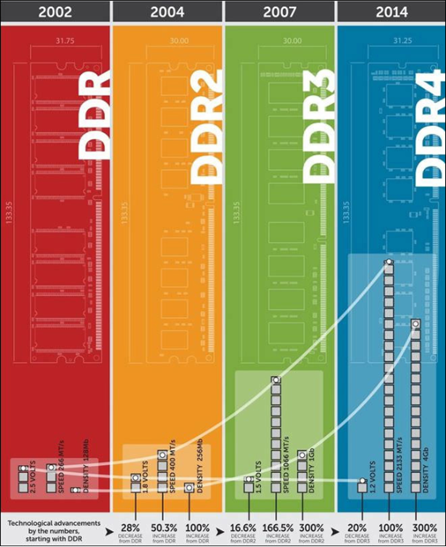

随着科技进步加速,新型 DDR4 及 DDR5 已广泛运用市场。预计在不久将来,更为先进的内存模块设计将呈现出高度智能化和集成化趋势,以提升传输速率与稳定性。