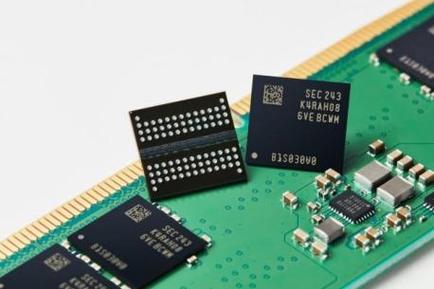

DDR2布线规则的重要性

DDR2作为常见的双数率同步动态随机存取存储器(SDRAM)被广泛用于各类电子产品,如电脑。在制定并实施DDR2的线路布局时,遵守特定的电路规则极其关键。首先,严谨的线路安排能为稳定可靠的信号传输提供保障,降低。其次,规矩的布线有助于大幅增进系统效能,缩减能耗,显著提升整个设备的运作效果。因此,对DDR2的线路规则进行深度理解及掌握,对保障系统正常运转以及实现性能优化至关重要。

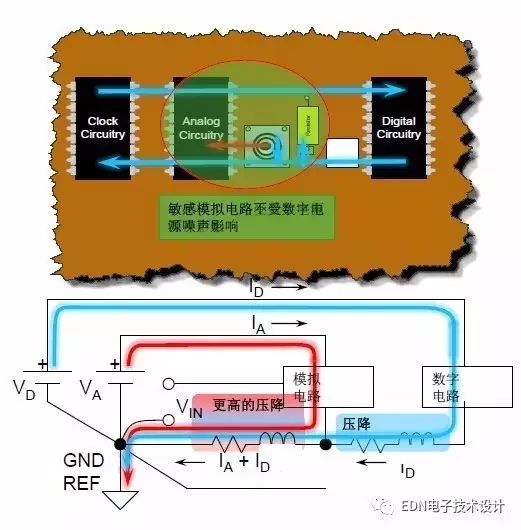

电路板设计与布线规则

在实施DDR2布线之际,应首要考虑电路板设计。优秀的电路板设计能筑牢后续布线工作之基石。合适选取电路板原料、层数及走线策略均会对原始系统效能带来莫大影响。在布线阶段,务必留意信号与电源线并行布置以消减相互干涉,同时需关注信号走线长度、路径及阻抗匹配等关键因素,以保障信号传输品质。

差分对与匹配长度

DDR2内部分别采用差动信号传送技术,故在布局网络电缆时务必要关注各差分对间的匹配度,若存在对不上的状况,将直接致使信号走样及产生串扰,从而影响系统性能。在此布局过程中,应尽最大化保持差分对长度相等,缩小学生产差分对之间的时间延迟差。同时,进行远距离传输时,亦需考量信号的功率损耗情况,制定相应的补救策略,以确保信号的完整性不受损。

终端电阻与终端电压

在DDR2电路设计过程中,终端电阻与电压的设定无疑是重要环节之一。其中,终端电阻主要为降低线路阻抗、抵制反射及波形失真,起到匹配作用;而终端电压则作为信号接收参考基准,对保证信号精准传递有着关键性影响。因此,在实践中应当依据特定环境选择最佳的终端电阻值与理想电压水平,从而最大程度提升信号传输质量。

时序约束与延迟控制

DDR2是一种同步动态随机存取存储设备,其有效布线必须充分顾及时刻约束与迟滞调控。定时管制设定了各类讯号在各时段内的需求,如建立时间与维持时间等关键指标;而延迟调控则关注信号传递过程中的耗费时间。科学设定定时约束与延迟调控,能保证数据实时准确地送达目的地,并满足存储器内置的操作标准。

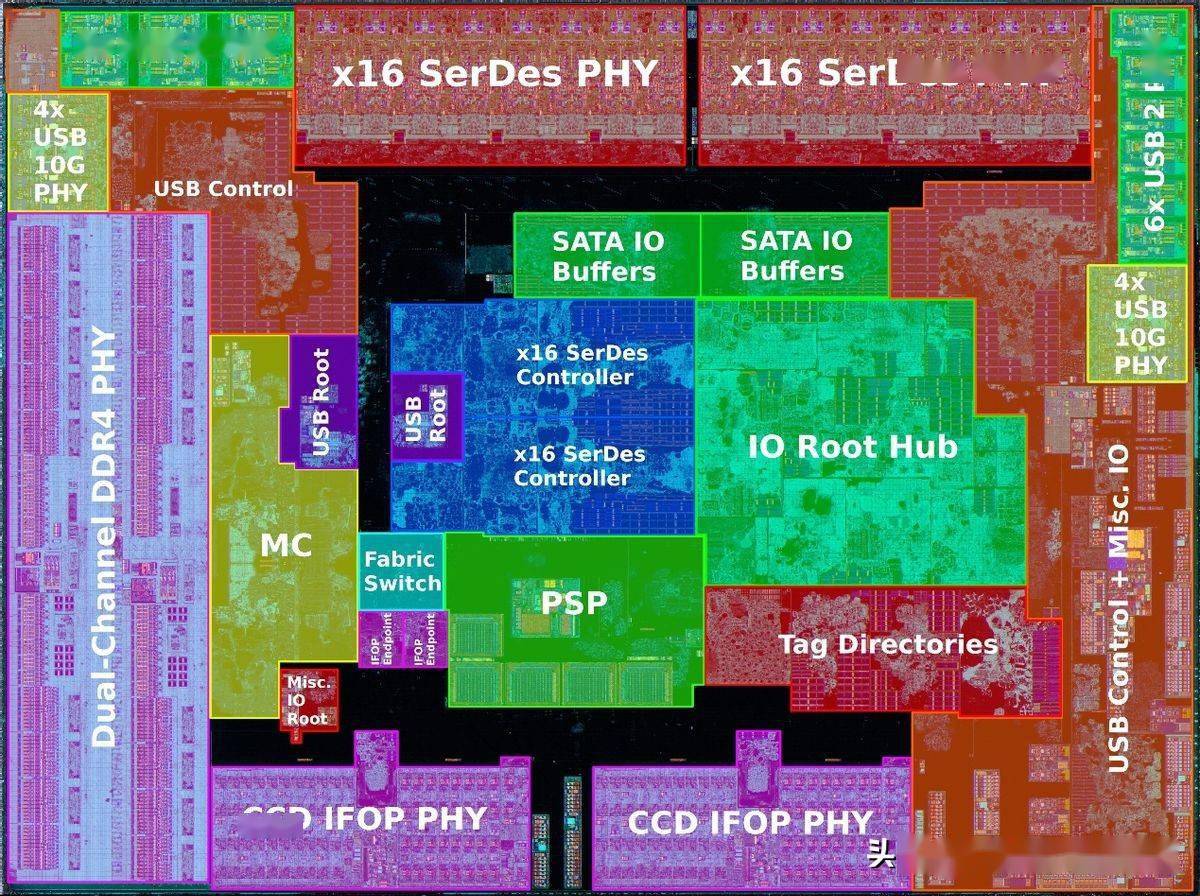

层间穿越与地孔设计

在多层PCB设计中,层间穿越与地孔设计对DDR2布线品质至关重要。层间穿越是借助各层之间的连线实现信号传输;地孔则负责联通不同区域以构建稳健的接地环境。合理规划层间穿越及地孔设计,能缩短信号回流路线,减轻串扰噪声,从而提升系统总体抗干扰性能。

仿真验证与调试优化

最后阶段,完成DDR2线路布局之后,仍需执行仿真验证与调试优化程序。利用仿真软件模拟现实任务环境中的信号传播状况,识别潜在问题并实时优化调节;同时参考实际测量数据对于系统效能进行评价,依据需求进一步修订设计策略。唯有通过持续的仿真验证与调试优化操作,方能够确保DDR2系统稳健且高效地运行。