什么是DDR3 Leveling技术

DDR3级联技术,即内存控制器中的关键技术之一,主要应对信号失真及时序不规范问题。伴随计算机系统演进及内存容量增大,DDR3级联技术的作用愈发显著。其功能在于调整内存控制器输出信号,确保数据能准确且稳定地传输至对象设备。此技术可增强存储细节传输的可信度与稳定性,从而提升整个系统运行效能。

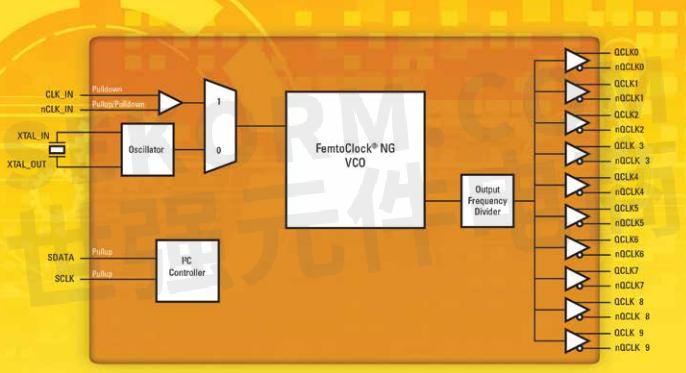

DDR3 Leveling技术包含写入与读取级别修正两大部分,分别应对数据写入与读出的控制。写入级别修正通过调整写入时钟相位保证数据准确写入内存;读取级别修正则调整读取时钟相位保障数据安全无误地读取出来,两部分相互促进,提升了DDR3内存控制器的稳定性及其效率。

DDR3 Leveling技术的原理

DDR3 Leveling技术系根据内存控制器对数据信号实行采样与修正而设计。数据传输期间,因信号传递路径长度及阻抗之诸多原因导致信号变形与时序偏离,进而影响数据准确性。为应对此类现象,DDR3 Leveling技术通过持续调整时钟相位,确保数据信号能在接收终端得到精确采样与解析。

在写入级联校正过程中,内存控制器依据预设模式,发出控制信息,引发内存模组进行采样,从而借助分析采样结果来锁定最优的写入时钟相位,进而运用于实际数据传输当中。同样,在读取级联校正操作中,内存控制器下达读指令,静待内存模组反馈数据,然后通过分析反馈数据的时序特性,精准调整读取时钟相位,以保证数据能准确无误地被接受到。

DDR3 Leveling技术的优势

DDR3等级制度技术凭借其诸多优点,已然成为了现代计算机系统中的核心组成。该技术精准设定及时钟相位,成功削弱了信息失真与时序偏移问题导致的影响,极大提升了内存传输效能的可靠度及稳定性。此外,该技术还能应对不同工作环境中各类复杂的电磁干扰和噪音情况,使得系统能在各种极端状况下保持正常运行。

此外,DDR3级联技术还能提升系统性能与能耗效率。精确调整时钟相位可大大减少因数据错传引发的重传次数,进一步提升整体效率。同时,精调时序参数既保障高可靠性又优化了功耗,养护设备使用寿命。

如何实现DDR3 Leveling技术

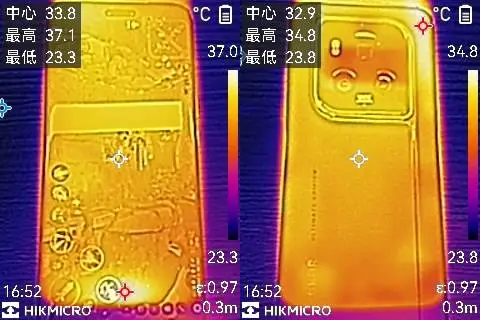

为实现DDR3 Leveling技术,需从硬件与软件两方面进行综合考量。硬件层面,需关注PCB布线、电源分配以及阻抗匹配等要素对信号质量的潜在影响;同时,选用优质且具有低延迟特性的元件以保障优秀的信号传递性能。而在软件层面,需编撰精密的算法以支持自动校正功能的执行,并持续调整以适应各种复杂工况所需。

实践过程中,须借助各类测验设备实施实时监控与调整,以核实DDR3水平对齐技术运行结果是否符合预期效应。通过持续性的测试及参数调整,可进一步提升DDR3内存控制器的效能及其稳定性。

未来发展趋势

随着计算机体系对信息传递的需求日益提高,并受到 DDR4 与 DDR5 全新内存标准普及的影响,DDR3 平滑调整技术亦需随之升级以应对挑战。在未来,我们预计其对高频率、大容量以及低能耗的追求将更为严格。

面对日益加速的人工智能、云计算和物联网等新科技领域的崛起,DDR3 Leveling技术仍将扮演不可或缺的角色,与其他尖端科技相互融合,共同推进计算机系统性能的持续进步。

结语

总而言之,作为关键的内存控制技术,DDR3 Leveling对于当下计算机系统有着举足轻重的作用。其精准调节时钟相位、解决信号失真的功能提升了内存传输效率及稳定性,进而赋予电脑系统众多优势。随着科技进步以及市场需求的变动,有充分理由期待此技术不断提高继续发展,并为未来电脑系统带来更多灵活性及创新性。