了解AR9331 DDR

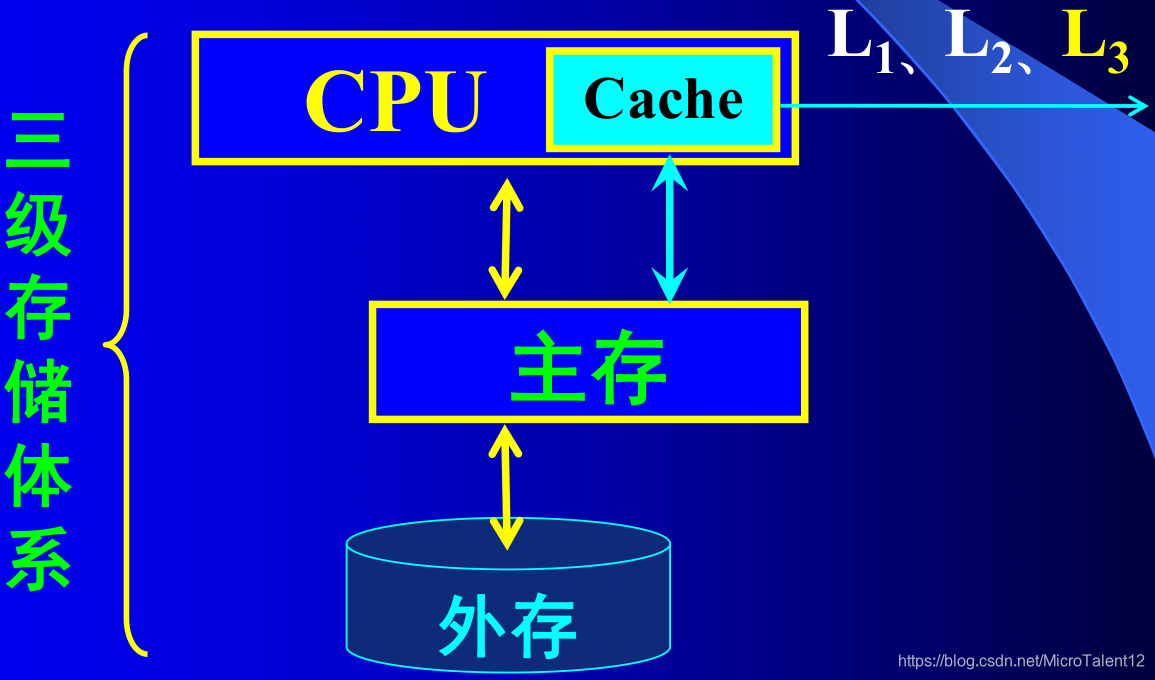

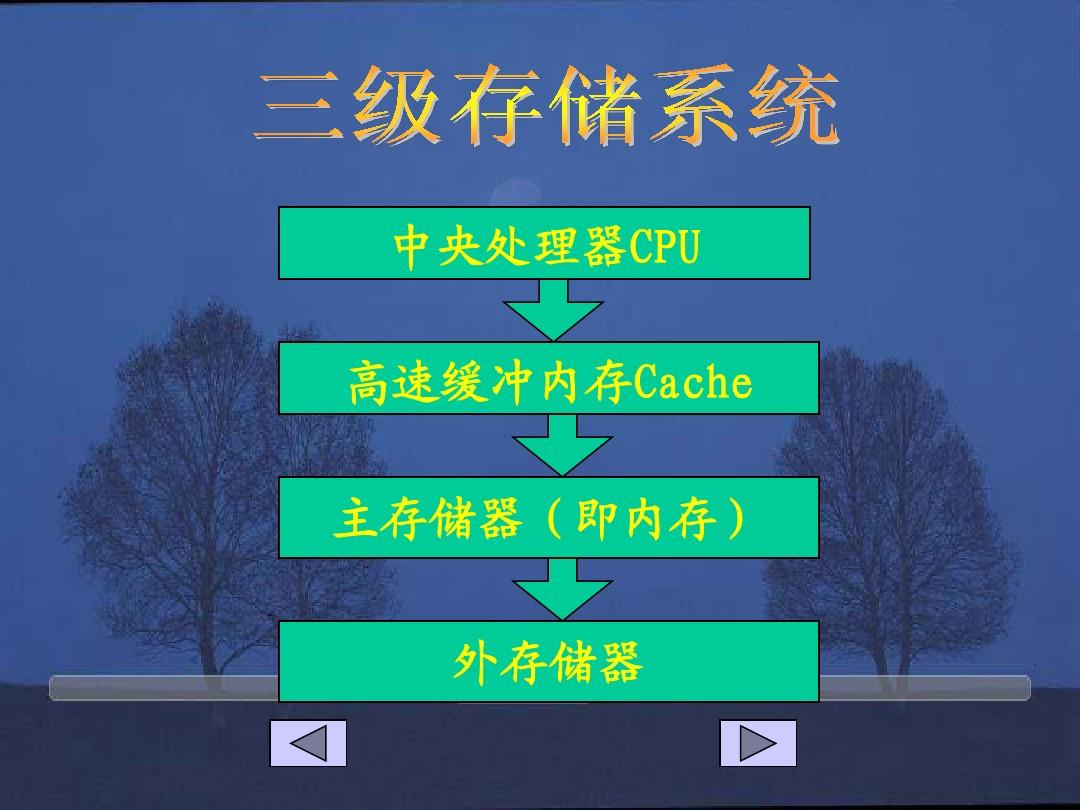

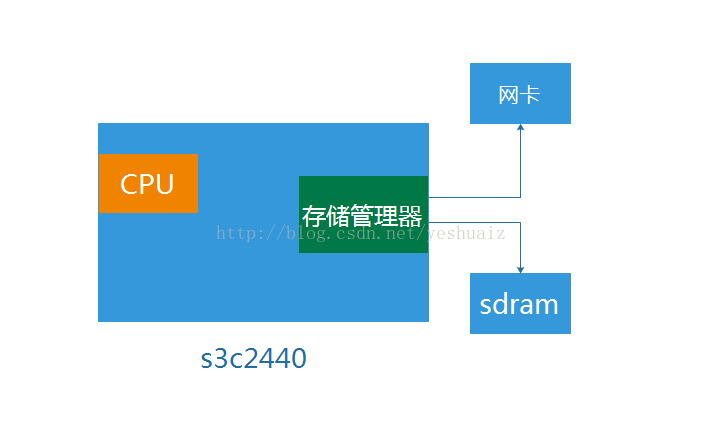

高通公司研发的AR9331处理器芯片已广泛应用于无线网路设备与智能家庭用品。此外,DDR(双倍数据速率)内存是现代电脑系统的主要存储形态,具备快速读写能力。在此环节中,AR9331的DDR内存控制器发挥了重要角色,保障了处理器与内存间的流畅通信。

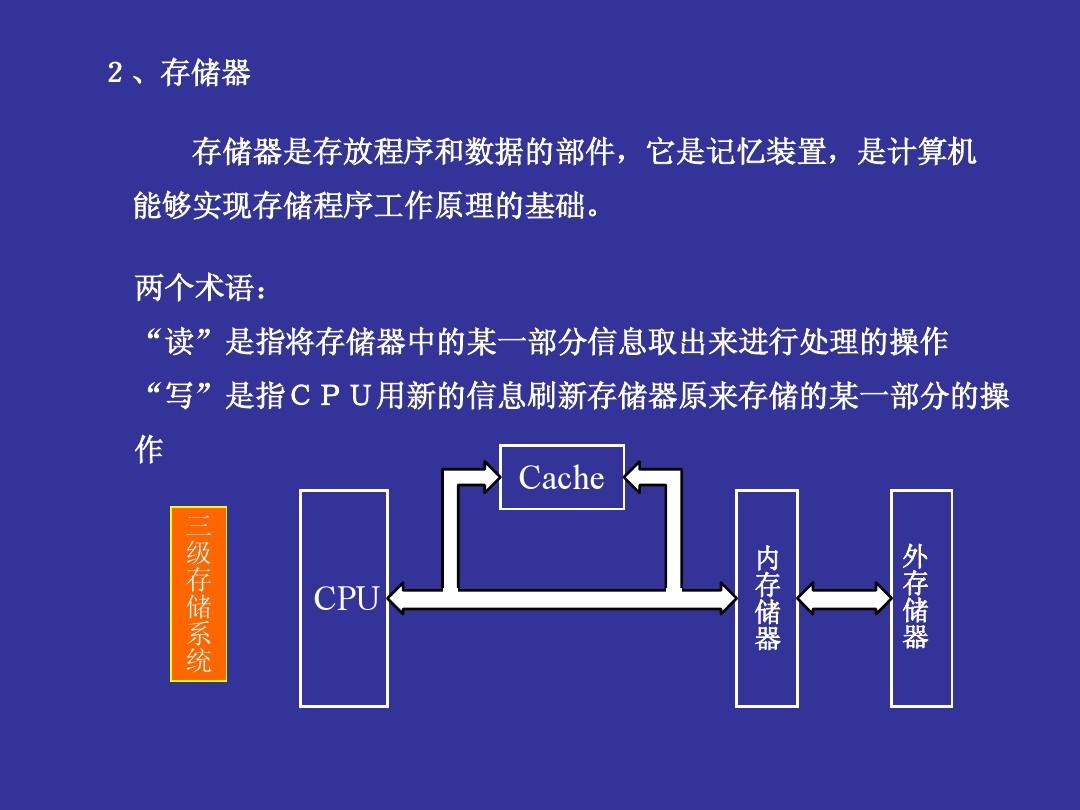

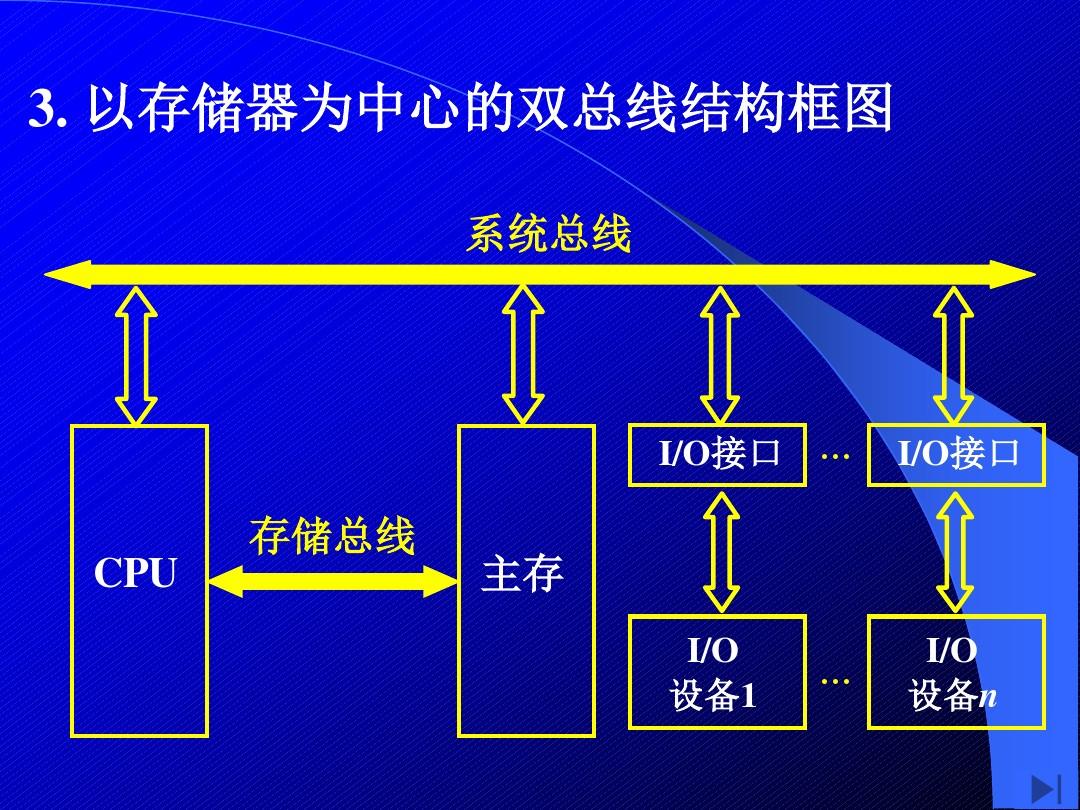

AR9331处理器通过DDR内存控制器与DDR内存进行信息交互,实现读取、写入以及程序、数据的处理。这种内存控制器在此过程中有着无法替代的重要性,它负责处理各种内存访问请求及控制数据传输时间顺序等复杂任务,对设备的效率和整体性能产生深远影响。

DDR内存工作原理

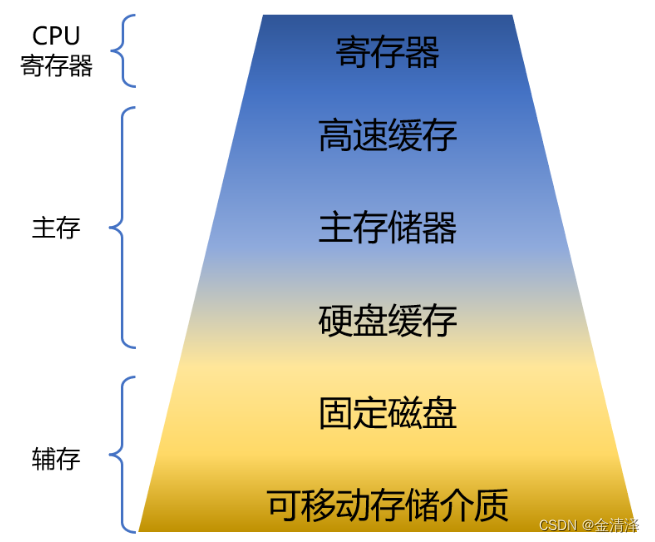

DDR内存搭载双倍数据传输速率技术,能够在古典时间周期内传输两轮数据,相较于单倍数据速率的SDR内存,展现出更为优异的数据处理性能。为了确保正常运作,DDR内存需要适当控制时序,这其中包含了预充电、启动、读取以及写入等众多环节。每个指令皆由DDR内存控制器负责生成并下达。

读取环节中,AR9331处理器凭借高效的DDR内存控制器,输出相应地址和控制信号给DDR内存模组,启动各项操作,迅速将数据传输至处理器。反之,在存储阶段,所需数据进入DDR内存模组得以妥善保存,保证了数据管理的稳定性与可靠性。然而,上述两种操作皆需要精确的协同配合与时序控制,以确保信息的精确度与稳定性。

AR9331 DDR内存控制器架构

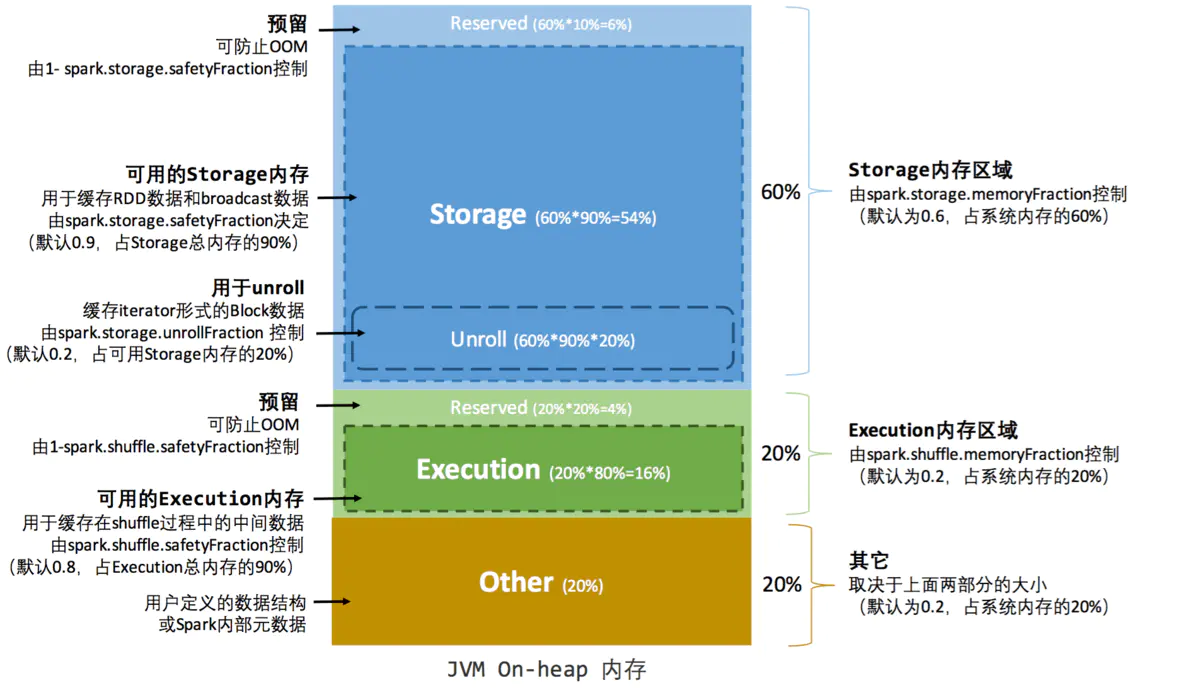

ARC5820 LPDDR4 存储器控制器主要包含地址生成、数据缓冲以及时序控制模块。其中,地址生成逻辑协助转换和传递处理器输入地址信号为适配 DDR 内存识别所需的行列地址格式;数据缓冲器提供对重要读/写数据的临时存储空间;时序控制单元负责控制各项时序信号的正常运作,从而确保数据传输过程符合预定标准流程。

不仅如此,采用AR9331 DDR内存控制器的双核系统,配备了先进的故障侦测和纠正(ECC)技术,有效规避了因硬件问题导致的数据误判,进而大幅提升了系统运作的稳定性和稳健性。

优化AR9331 DDR性能

针对提升AR9331 DDR系统性能的问题,可以从以下几方面进行精细化调整:

1.时序优化:合理调整时序参数,确保信号传输稳定可靠;

2.数据缓冲优化:增加适量的数据缓冲区可以提高读写效率;

3. ECC功能应用:开启ECC功能可以提高系统容错能力;

内层总线带宽提升策略:科学设定总线架构,促进数据高效流通。

芯片线路优化设计:精妙安排芯片内模块间的连线布置。

应用领域与未来发展

随着物联网技术行业的快速发展,对低功耗高性能设备的需求日渐增加。针对无线路由器、智能家居、工业自动化等领域,AR9331 DDR存储器展现了显著的应用价值。

随着诸如人工智能、自动驾驶及智能医疗等新兴科技的快速崛起,对高效且稳定的CPU与存储器通讯性能的需求必将日益凸显。在此背景下,AR9331 DDR内存将继续发挥其重要作用,不断优化以满足新一轮市场需求。