了解DDR3自刷新技术

在当今电子产品领域,DDR3内存作为一款常用品种,其独特的自刷新功能乃保持内存正常工作不可缺少的一环。DDR3内存在运行时需不断更换所存数据,确保信息稳定且精准。此项技术乃DDR3内存持久可用的保障,自动刷新过程能防止数据遗失或损毁现象发生,进而提升内存性能与稳定性。

DDR3动态刷新的原理在于其内置的制导逻辑能果断地频繁刷写内存储存区域,由此防止了数据在结构中的散逸或者出现误差。在DDR3内存系统中,每一个存贮单元都有可能逐渐丧失存贮的数据,若未及时被刷新,便可能造成数据丧失或者读取的谋差。因此,DDR3内存芯片采用周期性的自我刷新动作,果断更新存储单元,使得数据得以保持完整并保证其精度。

DDR3的自刷新功能,主要依靠其复杂的内置逻辑及时序把握电路来实现。透过精巧的时序掌握与信号调整,每颗DDR3内存颗粒能依据精准时间施行自刷新动作,确保存储单元时刻保持最优状态。这一严谨精密之调控体系,确保DDR3在长期运转下仍然能维持优质性能表现。

DDR3自刷新技术原理

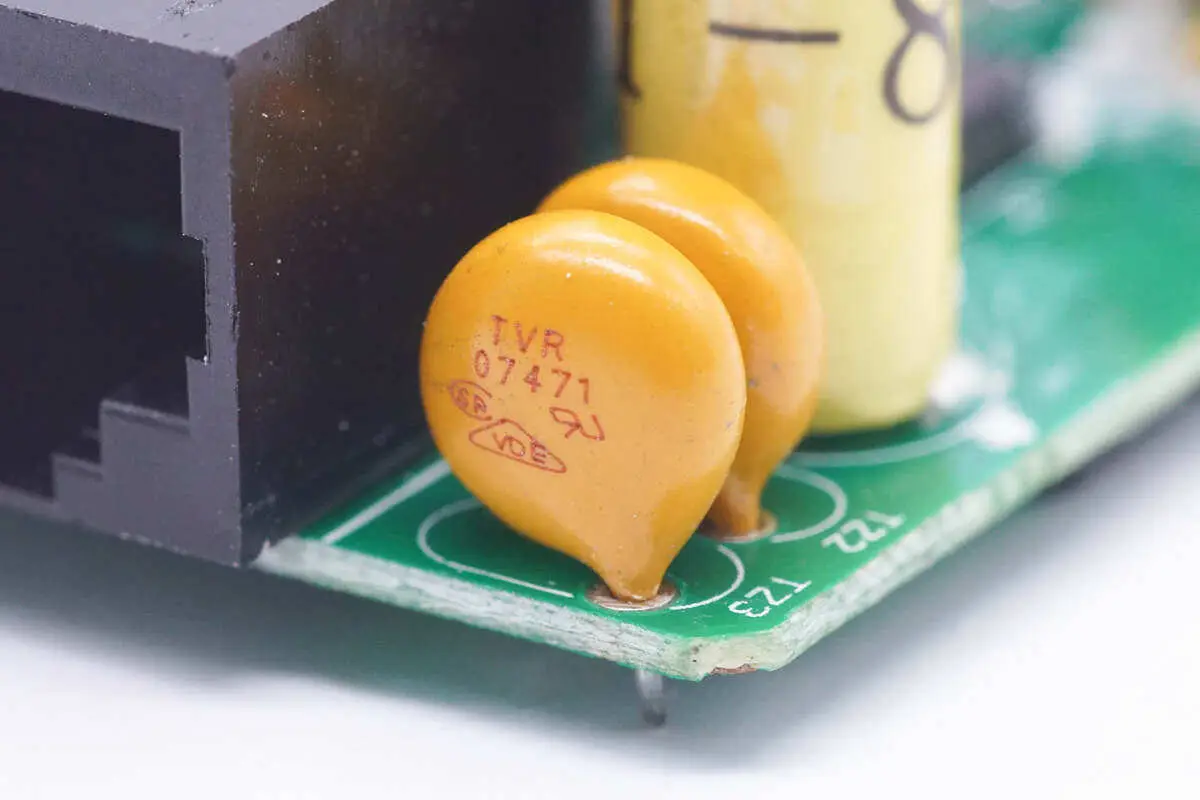

本文介绍了DDR3自刷新技术的基本理论,该技术以半导体物理特性与电子学原理为基础设计制造。DDR3内存芯片中的每个存储单元皆由电容阵列组成,用以绑定电荷以便存贮数据信息。我注意到,诸位对于电容的性质及其受外界环境影响而流走电能这一事实感到困惑,这可能在长期应用过程引发数据丢失或误差问题。

为解决此难题, DDR3 RAM采用自动刷新的先进技术。原理利用内置控制逻辑定期发出特别信号给各个储存单元,在约定的时间周期内在重新启动电容的同时,以前保留的资料便可进行重新写入。这样一来,就能确保数据的完整性与精确度,防止数据丢失乃至损害。

除此之外,为进一步提升自身刷新技术的优势,实际运用中还引入了其他相关措施进行辅助。举例来讲,在设计DDR3内存芯片的过程中,通过充分评估诸多外界环境变量如温度和电压对电容电荷保存与释放速率的影响,进而采用针对性的调整策略以提升自动刷新的效率和稳定性,使其能更优质地发挥效用。

优化DDR3自刷新技术

在科技进步及需求升级的背景下,自刷新技术需要适应DDR3的更高要求。为了增强DDR3内存芯片的耐用性、稳定度以及提高性能,研究人员持续优化改良该技术,并探索创新途径以应对这些挑战。

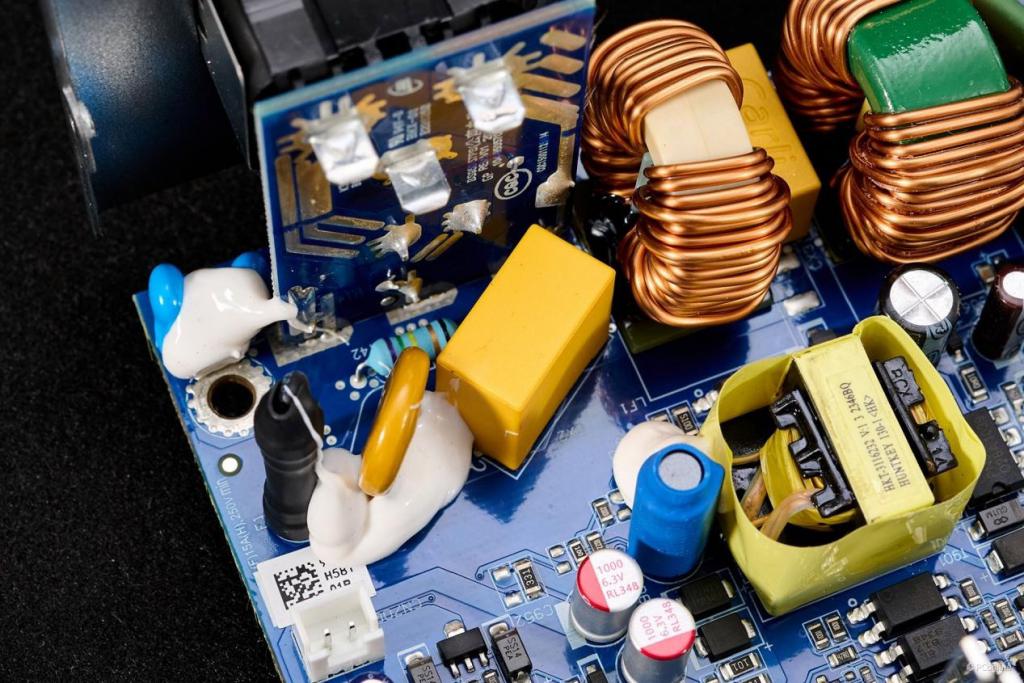

首先,在硬件设计层面,可通过改善电路结构与升级材料工艺,从而提升DDR3芯片的自我刷新的效率。比如选择低能耗材质,优化弄装置局以降低能源消耗,增强稳定性。此外,针对外部噪音和干扰的抵抗能力也应予以强化。

其次,可从软件算法层面,优化控制逻辑及升级调度算法,从而提升DDR3芯片自刷新精确度与速率。如选用智能调度策略,灵活调整参数,依实时状况调整刷新策略以提高效益;利用AI、大数据分析等新兴科技进一步优化自刷新过程亦颇具价值。

此外,借助于系统集成技术,我们能够采取诸如协调配合其它硬件设备、调整总线构造等措施来优化整个系统的表现。如,在处理信息时,与其配套的处理器、显卡等设备共同协作,有针对性地改进总线通信协议以提高系统的运作效能。同样地,与操作系统、驱动程序等相关软件的完美结合,对于增强系统稳定性亦大有助益。

未来展望与挑战

伴随信息化进程和科技创新的推进,DDR3自刷新技术面临新机遇及挑战。在可持续能源与智能应用日益被重视的当下,用户正对DDR3内存芯片提出更高期望。

首要目标是通过节约能耗和避免资源浪费等手段,改善环境恶化问题,推动可持续的经济增长模式。因此,DDR3自刷新技术需进一步完善节能优化,争做生态友好型产品,同时与创新材料及工艺相融合,从而提高产品效益。

其次,在智能化应用领域,人们期望借助如人工智能及物联网这样的先进科技,将DDR3存储器芯片与各类设备紧密链接起来,实施智能化管理及运用。可见,未来DDR3自刷新技术需更加智能、灵活且支持多元化的应用场景需求。

虽然DDR3自刷新技术已取得显著进展且在各大设备上得到广泛应用,然而它仍需应对各种挑战及机遇。优化提升并结合新技术趋势的发展是它满足未来需求的关键策略。